儈僯僐儞偺俫俬俿俙俠侾侽傪丂俽俹俙俼俿俙俶俁偱幚尰丄偦偺侾丂僋儘僗傾僙儞僽儔

2010.5.16 峏怴 OML, MASS 僥乕僾僀儊乕僕丄幨恀捛壛

慺悢傪媮傔傞僜僼僩傪俫俬俿俙俠侾侽偺傾僙儞僽儔偱彂偔

僄儔僩僗僥僱僗偺饪偄偲偄偆柤偺僜僼僩傪俫俬俿俙俠侾侽偺傾僙儞僽儔偱彂偄偰傒傑偡丅俥俹俧俙偱俫俬俿俙俠侾侽傪嶌傞偺偼丄婎杮峔惉偺係俲倂乮俉俲僶僀僩乯側偺偱丄偙偺儊儌儕撪偱儚乕僋僄儕傾偲僾儘僌儔儉偑擖傞傕偺偲偟傑偡丅偙偺偨傔丄媮傔傞儚乕僋僄儕傾傪俀俆俇侽屄妋曐偟偰丄偙偺攞悢丄俁乣俆侾俀侽傑偱偺慺悢偲偄偆偙偲偵側傝傑偡丅側偤俁偐傜側偺偐偼丄僄儔僩僗僥僱僗偺饪偄偲偄偆僜僼僩偱偼丄侾偼埫栙偵懚嵼偡傞慺悢偲偟偰巆傝傪媮傔傞傛偆偵側偭偰偄傞偐傜偱偡丅

XASM HITAC10 ver. 1.01 (Bitcraft )

0000 // SIEVE

0200 ORG X"200"

0200 0A39 BGN L BUF

0201 3A3A ST BCNT

0202 0A3B L M819

0203 3A42 ST CNT

0204 0A40 L N1

0205 3E3A L1 ST ,I BCNT

0206 523A KCT BCNT

0207 5242 KCT CNT

0208 4205 B L1

0209 // HLT

0209 //

0209 0A41 L Z0

020A 3A43 ST CNTI

020B 3A3E ST CONT

020C 0A3B L M819

020D 3A42 ST CNT

020E 0A39 L BUF

020F 3A3A ST BCNT

0210 0E3A L4 L ,I BCNT

0211 6862 KNA

0212 4227 B L2

0213 0A3F L N3

0214 1243 A CNTI

0215 1243 A CNTI

0216 3A44 ST PRIM

0217 1243 A CNTI

0218 3A45 ST K

0219 0A3C L5 L N819

021A 1A45 S K

021B 6864 KPA

021C 4226 B L3

021D 0A39 L BUF

021E 1245 A K

021F 3A3D ST CLRP

0220 0A41 L Z0

0221 3E3D ST ,I CLRP

0222 0A44 L PRIM

0223 1245 A K

0224 3A45 ST K

0225 4219 B L5

0226 523E L3 KCT CONT

0227 5243 L2 KCT CNTI

0228 523A KCT BCNT

0229 5242 KCT CNT

022A 4210 B L4

022B 6F00 HLT

022C 0A39 L BUF

022D 3A3A ST BCNT

022E 0A3B L M819

022F 3A42 ST CNT

0230 0A41 L Z0

0231 3A43 ST CNTI

0232 0E3A L6 L ,I BCNT

0233 6842 KZA

0234 5243 KCT CNTI

0235 523A KCT BCNT

0236 5242 KCT CNT

0237 4232 B L6

0238 6F00 HLT

0239 0400 BUF DC X"400"

023A 0001 BCNT DC 1

023B F600 M819 DC -2560

023C 0A00 N819 DC 2560

023D 0000 CLRP DC 0

023E 0000 CONT DC 0

023F 0003 N3 DC 3

0240 0001 N1 DC 1

0241 0000 Z0 DC 0

0242 0000 CNT DC 0

0243 0000 CNTI DC 0

0244 0000 PRIM DC 0

0245 0000 K DC 0

0246 END BGN

0246

0246

僋儘僗傾僙儞僽儔 ash10.exe 偲丄慺悢傪媮傔傞僜僼僩偺僼傽僀儖

儈僯僐儞偺俫俬俿俙俠侾侽傪丂俽俹俙俼俿俙俶俁偱幚尰丄偦偺俀丂婎斅偲夞楬

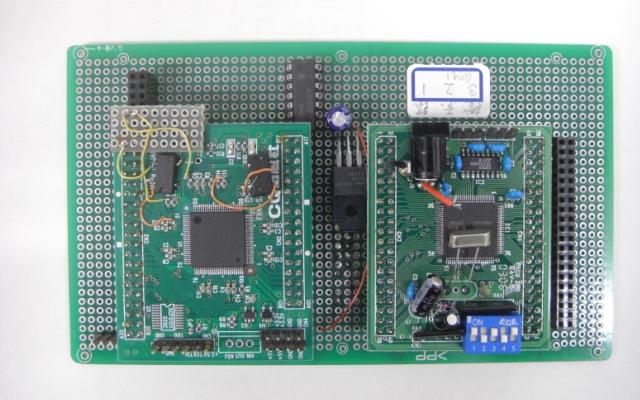

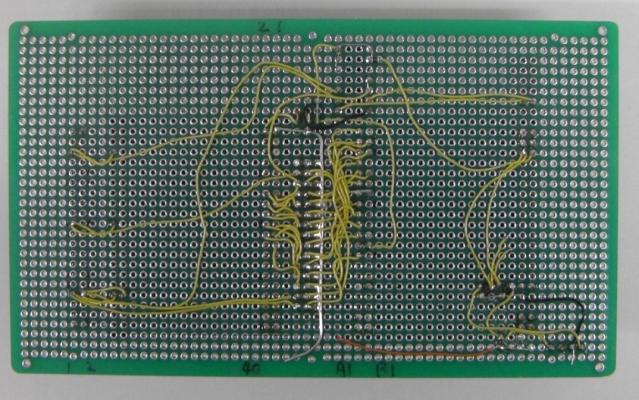

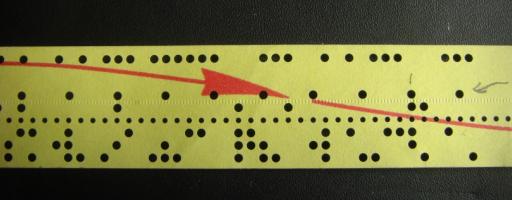

俫俉俁侽俇俋乮塃丄廐寧揹巕捠彜乯 傪偺偣偰愙懕偟偰偄傑偡丅塃偼丄儅僓乕儃乕僪偺棤柺攝慄偱偡丅

儅僓乕儃乕僪偺夞楬恾偼偙偪傜丅乮丂俽俹俙俼俿俙俶俁婎斅偲俫俉俁侽俇俋婎斅偼徣棯丂乯

俫俬俿俙俠侾侽偺弌椡億乕僩丂亅亅亜丂俫俬俿俙俠侾侽偺億乕僩儗僕僗僞乮俥俹俧俙撪乯丂亅亅亜丂俫俉俁侽俇俋偺儊儌儕

俫俉俁侽俇俋偺儊儌儕丂亅亅亜丂俫俬俿俙俠侾侽偺億乕僩儗僕僗僞乮俥俹俧俙撪乯丂亅亅亜丂俫俬俿俙俠侾侽偺擖椡億乕僩

俫俬俿俙俠侾侽偺昞帵丂亅亅亜丂俥俹俧俙撪偵愝偗偨儗僕僗僞丂亅亅亜丂俫俉俁侽俇俋偱撉傓丅

俫俉俁侽俇俋偱彂偔丂亅亅亜丂俥俹俧俙撪偵愝偗偨儗僕僗僞丂亅亅亜丂俫俬俿俙俠侾侽偺僐儞僜乕儖

埲忋偺傛偆偵丄僆儕僕僫儖偺俫俬俿俙俠侾侽偵晅偄偰偄傞昞帵傗丄惂屼僗僀僢僠丄俬乛俷偼丄偡傋偰俥俹俧俙撪偵愝偗偨儗僕僗僞偱戙梡偟傑偡丅巊梡偟偰偄傞俽俹俙俼俿俙俶俁偑傕偭偲戝偒偔丄僺儞悢偑懡偗傟偽丄僆儕僕僫儖偺俫俬俿俙俠侾侽偺傛偆偵丄僨乕僞昞帵傗僷僱儖僗僀僢僠傪巊偭偰丄杮暔偺傛偆偵憖嶌偡傞偙偲傕壜擻偱偡丅

儈僯僐儞偺俫俬俿俙俠侾侽傪丂俽俹俙俼俿俙俶俁偱幚尰丄偦偺俁丂偡傋偰俫俉俁侽俇俋偱憖嶌

僐傾儊儌儕 偱丄崅懍偺僼儔僢僔儏儊儌儕傒偨偄側傕偺側偺偱丄揹尮傪愗偭偰傕撪梕偼徚偊傑偣傫丅儊儌儕偵僨乕僞傪彂偔偵偼丄慜柺偵偮偄偰傞憖嶌僗僀僢僠偱丄侾俇價僢僩偺儅僔儞岅偱捈愙彂偒傑偡丅堦斣嵟弶偼丄俬俹俴偲屇偽傟傞侾俇岅傎偳偺抁偄僾儘僌儔儉傪丄侽斣抧偐傜僗僀僢僠偱侾俇價僢僩扨埵偱彂偒傑偡丅

俫俬俿俙俠侾侽偺儊僀儞儊儌儕偼嵟掅尷偺係俲倂偲偡傞丅乮俽俹俙俼俿俙俶俁偺僽儘僢僋俼俙俵傪係屄巊偆乯

俫俬俿俙俠侾侽傪俽俿俷俹偡傞丅

俫俬俿俙俠侾侽傪巜掕傾僪儗僗偐傜俼倀俶偡傞丅

俫俬俿俙俠侾侽偺侾俇價僢僩僷僱儖僗僀僢僠傪愝掕偡傞丅

俫俬俿俙俠侾侽傪巜掕傾僪儗僗偐傜侾柦椷幚峴偡傞丅

俫俬俿俙俠侾侽偺尰嵼偺忬懺傪撉傓丅俼倀俶丄俽俿俷俹丄晅壛柦椷偱妱傝崬傒丄俠俙俼俼倄

俫俬俿俙俠侾侽偺柦椷幚峴偵梫偟偨僋儘僢僋悢傪撉傓丅

俫俬俿俙俠侾侽偺儗僕僗僞傪撉傓丅

俫俬俿俙俠侾侽偺儊儌儕偺傾僪儗僗傪愝掕偡傞丅愝掕屻丄撪梕傪撉傒弌偣傞丅

俫俬俿俙俠侾侽偺儊儌儕偵僨乕僞傪彂偔丅

俫俬俿俙俠侾侽偺俬乛俷柦椷偺僼儔僌傪憖嶌偡傞丅俫俉偲俫俬俿俙俠侾侽偲偺僴儞僪僔僃僀僋丅

埲忋偺婡擻傪丄偱偒傞偩偗俫俉偺傾僪儗僗嬻娫傪巊傢偢偵幚尰偡傞偨傔丄傾僪儗僗傪俁杮傪巊偄丄僨乕僞僶僗偼俉價僢僩偲偟傑偡丅乮俫俉俁侽俇俋婎斅偺奜晹僨乕僞僶僗偑俉杮乯

昞侾丂憖嶌儗僕僗僞

俫俉傾僪儗僗 丂柤徧丂 儕乕僪撪梕 儔僀僩丂

侽倶俇侽侽侽侽侽 H10PCH 僾儘僌儔儉僇僂儞僞MSB 俉價僢僩 侾柦椷幚峴

侽倶俇侽侽侽侽侾 H10PCL 僾儘僌儔儉僇僂儞僞LSB 俉價僢僩 俼倀俶

侽倶俇侽侽侽侽俀 H10ACH 傾僉儏乕儉儗乕僞MSB 俉價僢僩 俬乛俷僶僢僼傽乕偵彂偔

侽倶俇侽侽侽侽俁 H10ACL 傾僉儏乕儉儗乕僞LSB 俉價僢僩 壗傕偟側偄

侽倶俇侽侽侽侽係 H10DBH 儊儌儕撪梕MSB 俉價僢僩 壗傕偟側偄

侽倶俇侽侽侽侽俆 H10DBL 儊儌儕撪梕LSB 俉價僢僩 婡擻憖嶌 stepc 昞俀嶲徠

侽倶俇侽侽侽侽俇 PSWITCHH 幚峴拞 僄儔乕 妱傝崬傒 側偳 俫俬俿俙俠侾侽偺僷僱儖僗僀僢僠MSB 俉價僢僩

侽倶俇侽侽侽侽俈 PSWITCHL 俫俬俿俙俠侾侽弌椡抣 俫俬俿俙俠侾侽偺僷僱儖僗僀僢僠LSB 俉價僢僩

昞俀丂婡擻憖嶌 stepc

彂偔撪梕丂俁價僢僩 丂柤徧丂 摦嶌 旛峫丂

侽倶侽侽 俶俷俹 壗傕偟傑偣傫 侽埲奜偺愝掕偱幚峴屻偵帺摦揑偵侽偵側傞

侽倶侽侾 僙僢僩儊儌儕傾僪儗僗 僷僱儖僗僀僢僠偺抣傪儊儌儕傾僪儗僗偵愝掕 儅僔儞僗僥乕僩 state 偑侽偺偲偒偺傒婡擻偡傞

侽倶侽俀 俶俷俹 壗傕偟傑偣傫 侽埲奜偺愝掕偱幚峴屻偵帺摦揑偵侽偵側傞

侽倶侽俁 俶俷俹 壗傕偟傑偣傫 侽埲奜偺愝掕偱幚峴屻偵帺摦揑偵侽偵側傞

侽倶侽係 僙僢僩僾儘僌儔儉僇僂儞僞 僷僱儖僗僀僢僠偺抣傪僾儘僌儔儉僇僂儞僞偵愝掕 儅僔儞僗僥乕僩 state 偑侽偺偲偒偺傒婡擻偡傞

侽倶侽俆 俶俷俹 壗傕偟傑偣傫 侽埲奜偺愝掕偱幚峴屻偵帺摦揑偵侽偵側傞

侽倶侽俇 儕僙僢僩俠俹倀 俫俬俿俙俠侾侽傪弶婜忬懺偵偟傑偡丅嫮惂掆巭 儊儌儕僒僀僘偺巜掕

侽倶侽俈 俶俷俹 壗傕偟傑偣傫 侽埲奜偺愝掕偱幚峴屻偵帺摦揑偵侽偵側傞

儈僯僐儞偺俫俬俿俙俠侾侽傪丂俽俹俙俼俿俙俶俁偱幚尰丄偦偺係丂儅僔儞僗僥乕僩愝寁

戙昞揑側儗僕僗僞丒儊儌儕墘嶼偺柦椷丄俴乮儘乕僪乯

俷俹僐乕僪丂俆價僢僩 僀儞僟僀儗僋僩巜掕 僛儘儁乕僕巜掕 傾僪儗僗丂俋價僢僩

侽侽侽侽侾 俬 倅 俙俙俙俙俙俙俙俙俙

晹暘姰惉

儅僔儞僗僥乕僩偺庬椶

僗僥乕僩斣崋 摦嶌撪梕侾 摦嶌撪梕俀 摦嶌撪梕俁

state 侽 儊儌儕昞帵傾僪儗僗傪儊儌儕傾僪儗僗偵弌偡 僐儞僜乕儖偐傜僗僞乕僩懸偪丅startp == 1 俠俹倀掆巭

state 侾 僾儘僌儔儉僇僂儞僞傪儊儌儕傾僪儗僗偵弌偡 儊儌儕偐傜偺 ready 懸偪丅ready 偱柦椷僨僐乕僪 柦椷僼僃僢僠丄僨僐乕僪丄師偺 state 寛掕

state 俀 state 1 偱丄娫愙傾僪儗僢僔儞僌偱丄儊儌儕傪撉傓 儊儌儕偐傜偺 ready 懸偪丅ready 偱 state = 3 僨乕僞僼僃僢僠丅侾僋儘僢僋偱 ready = 1

state 俁 儊儌儕傾僋僙僗 儊儌儕偐傜偺 ready 懸偪丅ready 偱 柦椷幚峴 柦椷幚峴丅丂state = 4

state 係 柦椷幚峴廔椆張棟 僗僩僢僾僼儔僌僠僃僢僋 僗僩僢僾偱側偗傟偽丄state = 1 偱師偺柦椷

hitac3s_14.v

僶僌偁傝 丂hitac3s.v

hitac3s.ucf 仼偑柍偄応崌偼塃hitac3s.txt

hitac3s14.sr 丂俫俉俁侽俇俋偺儊儌儕丄0x40E000 埲崀偵儘乕僪偟偰僐儞僼傿僊儏儗乕僔儑儞壜擻

僶僌偁傝 丂hitac3s6.sr 丂俫俉俁侽俇俋偺儊儌儕丄0x40E000 埲崀偵儘乕僪偟偰僐儞僼傿僊儏儗乕僔儑儞壜擻

hitac3s14.bit

僶僌偁傝 丂hitac3s6.bit

h10m69.c

makefile丂椺

h10m69.x丂椺

h10m69_22.mot丂0x400284 斣抧偐傜幚峴壜擻

massnoext4k.sr

dumpD.asm

儈僯僐儞偺俫俬俿俙俠侾侽傪丂俽俹俙俼俿俙俶俁偱幚尰丄偦偺俆丂奺庬偺柦椷幚峴

儅僔儞僗僥乕僩偺庬椶

柦椷 僗僥乕僩偺慗堏 摦嶌撪梕

儁乕僕撪儗僕僗僞丄儊儌儕娫偺墘嶼柦椷 侾亅亅亜俁

儁乕僕撪偺俋價僢僩偱傾僪儗僗偝傟傞儊儌儕偲墘嶼

僀儞僟僀儗僋僩儗僕僗僞丄儊儌儕娫偺墘嶼柦椷 侾亅亅亜俀亅亅亜俁

儁乕僕撪俋價僢僩偺儊儌儕偺撪梕傪傾僪儗僗偲偟偰偦偺儊儌儕偲墘嶼

儁乕僕撪僽儔儞僠柦椷 侾丂偺傒

儁乕僕撪偺俋價僢僩埲撪偱僽儔儞僠

僀儞僟僀儗僋僩僽儔儞僠柦椷 侾亅亅亜俀

儁乕僕撪偺俋價僢僩偺儊儌儕偺撪梕傪傾僪儗僗偲偟偰僽儔儞僠

儁乕僕撪僽儔儞僠丒傾儞僪丒儕儞僋柦椷 侾亅亅亜俁

儁乕僕撪偺俋價僢僩埲撪偱僒僽儖乕僠儞屇傃弌偟

僀儞僟僀儗僋僩僽儔儞僠丒傾儞僪丒儕儞僋柦椷 侾亅亅亜俀亅亅亜俁

儁乕僕撪偺俋價僢偺儊儌儕偺撪梕傪傾僪儗僗偲偟偰僒僽儖乕僠儞屇傃弌偟

儊儌儕僇僂儞僩傾僢僾丄僗僉僢僾柦椷 侾亅亅亜俁亅亅亜係

儁乕僕撪俋價僢僩偺儊儌儕偺撪梕傪亄侾偟偰侽側傜師偺柦椷傪僗僉僢僾

僀儞僟僀儗僋僩儊儌儕僇僂儞僩傾僢僾丄僗僉僢僾柦椷 侾亅亅亜俀亅亅亜俁亅亅亜係

儁乕僕撪俋價僢僩偺儊儌儕偺撪梕傪傾僪儗僗偲偟偰亄侾偟偰侽側傜師偺柦椷傪僗僉僢僾

俬乛俷柦椷 侾亅亅亜俁

巜掕偝傟偨俬乛俷偺擖弌椡傪峴偆丅僀儞僾僢僩偱偼俙俠偺壓埵俉價僢僩偑曄壔

俬乛俷忬懺敾掕僗僉僢僾柦椷 侾亅亅亜俁

巜掕偝傟偨俬乛俷偺忬懺傪敾掕偟偰師偺柦椷傪僗僉僢僾偡傞

傾僉儏乕儉儗乕僞墘嶼柦椷 侾亅亅亜俁

巜掕偟偨價僢僩悢偩偗俙俠傪僔僼僩偡傞丅侾價僢僩偁偨傝侾僋儘僢僋巊梡偡傞

傾僉儏乕儉儗乕僞僗僉僢僾柦椷 侾亅亅亜俁

傾僉儏乕儉儗乕僞偺忬懺傪敾掕偟偰師偺柦椷傪僗僉僢僾偡傞

俠俹倀忬懺曄峏柦椷 侾亅亅亜俁

妱傝崬傒嫋壜丄晄嫋壜側偳傪愝掕偡傞

俴俷俙俢丄俙俢俢柦椷

埲壓偼丄俴俷俙俢丄俙俢俢偺柦椷傪幚峴偟偨偲偒偺夞楬攇宍偱偡丅(N),乮MEM),(ADD)偼丄N 傗丄MEM 傗 ADD 偱傾僪儗僗偝傟傞儊儌儕偺撪梕傪帵偟傑偡丅maddr 偼丄儊僀儞儊儌儕偺傾僪儗僗偱丄侾僋儘僢僋屻偵偼撪梕偑 db 偵弌椡偝傟傑偡丅mb 偼 state 偑 1 偲 3 偺偲偒 db 傪儔僢僠偟偨傕偺偱偡丅丅state 偼丄侾丆俁偲側傝丄係僋儘僢僋偵側傝傑偡丅

夞楬僼傽僀儖丄hitac3s.v 偺儗僕僗僞

儗僕僗僞柤 婡擻 堄枴 摦嶌偺愢柧側偳

CLOCK 夞楬僋儘僢僋 棫偪忋偑傝偱桳岠( always@(posedge clk) ) 棫偪忋偑傝偱 state 偺慗堏傪敾掕

state 儅僔儞偺摦嶌忬懺傪巜掕偟傑偡 忬懺慗堏 ready,偦偺懠 偺抣偵傛偭偰丄摦嶌偑堎側傝傑偡

ready 侾偱儊僀儞儊儌儕偐傜偺僨乕僞偑妋掕 侾偱儊僀儞儊儌儕偺僨乕僞僶僗忋偺僨乕僞偑桳岠 state 1,2,3 偺応崌丄侽側傜侾偵偝傟傑偡

pc 僾儘僌儔儉僇僂儞僞 state = 1, ready = 0 偱丄僾儔僗侾偝傟傑偡 俴丆俙柦椷偱偼丄state = 1 偱忢偵師偺傾僪儗僗偵側傝傑偡

maddr 儊僀儞儊儌儕偺傾僪儗僗 柦椷傗丄僨乕僞傪撉傒弌偡傾僪儗僗抣 侾僋儘僢僋屻偵僨乕僞偑撉傒弌偝傟傑偡

db 儊儌儕偺僨乕僞僶僗 儊僀儞儊儌儕偐傜撉傒弌偝傟偨僨乕僞 儊僀儞儊儌儕偺傾僪儗僗妋掕偐偨忢偵侾僋儘僢僋屻偵妋掕

ac 傾僋乕儉儗乕僞 侾俇價僢僩墘嶼儗僕僗僞 俫俬俿俙俠侾侽婎杮峔惉偱偺墘嶼儗僕僗僞偼偙傟偺傒

僽儔儞僠柦椷

僽儔儞僠柦椷偲丄偦傟偵懕偔壛嶼乮俙乯柦椷丅僽儔儞僠柦椷偺丂state 偼丄侾丆偺傒偲側傝丄俀僋儘僢僋偵側傝傑偡丅

僀儞僟僀儗僋僩傾僪儗僢僔儞僌偱偺俴俷俙俢柦椷

僀儞僟僀儗僋僩傾僪儗僢僔儞僌偱偺俴俷俙俢柦椷偲丄偦傟偵懕偔壛嶼乮俙乯柦椷丅state 偼丄侾丆俀丆俁偲側傝丄俇僋儘僢僋偵側傝傑偡丅ma 偼丄僀儞僟僀儗僋僩傾僪儗僢僔儞僌偺応崌偵丄state 偑 2 偺偲偒丄db 傪儔僢僠偟偨傕偺偱偡丅ma 偼丄僀儞僟僀儗僋僩埲奜偱偼丄kct 柦椷偱巊傢傟傑偡丅乮 kct 偺攇宍偼屻弎 乯

儊儌儕僀儞僋儕儊儞僩媦傃僗僉僢僾柦椷丄俲俠俿

俫俬俿俙俠侾侽偱偺忦審暘婒偼丄僗僉僢僾柦椷偱敾掕偟傑偡丅忦審傪枮偨偡偲丄師偺柦椷傪幚峴偣偢丄僾儘僌儔儉僇僂儞僞偑丂亄俀丂偝傟傑偡丅忦審傪枮偨偝側偄応崌丄僗僉僢僾偣偢偵師偺柦椷傪幚峴偡傞偺偱丄偙偙偵俛乮僽儔儞僠乯柦椷傪抲偒傑偡丅埲壓偺恾偼丄忦審傪枮偨偟偨応崌偺攇宍偱偡丅俲俠俿柦椷偼丄巜掕偡傞儊儌儕乮俵俤俵乯偺撪梕傪亄侾偟偰丄侽偵側偭偨傜僗僉僢僾偡傞偲偄偆忦審敾掕傪峴偄傑偡丅幚峴僗僥乕僩偼丄侾丆俁丆係偲丄俁僗僥乕僩乮俇僋儘僢僋乯偵側傝傑偡丅偙偺恾偱丄hitacw 偼丄儊僀儞儊儌儕傊偺儔僀僩怣崋乮 active high ) 丄mbw 偼丄儊僀儞儊儌儕傊彂偔撪梕乮侾俇價僢僩乯偱偡丅偙偙偱偺儊儌儕儔僀僩偼丄侾僋儘僢僋偱廔椆偟偰偄傑偡丅

僒僽儖乕僠儞屇傃弌偟偺俛俙俴柦椷乮僽儔儞僠丒傾儞僪丒儕儞僋乯

俫俬俿俙俠侾侽偵偼僗僞僢僋億僀儞僞偑側偄偺偱丄栠傝斣抧偺奿擺応強偲偟偰丄僒僽儖乕僠儞偺愭摢斣抧傪巊偄傑偡丅偦傟偵懕偔俴俷俙俢乮俴乯柦椷丅state 偼丄侾丆俁偲側傝丄係僋儘僢僋偵側傝傑偡丅僒僽儖乕僠儞偺愭摢斣抧乮俽倀俛乯偵栠傝斣抧俶亄侾傪彂偒丄俽倀俛亄侾斣抧偺俴俷俙俢柦椷偐傜幚峴偟傑偡丅僒僽儖乕僠儞偐傜偺儕僞乕儞偼丄栠傝斣抧傪奿擺偟偰偄傞俽倀俛傪丄僀儞僟僀儗僋僩傾僪儗僢僔儞僌偱僽儔儞僠偟傑偡丅儕僞乕儞傪幚峴偡傞柦椷偼丄俛丂丆俬丂俽倀俛丂偲彂偒傑偡丅偙傟偱丄俽倀俛偵奿擺偝傟偨抣傪僾儘僌儔儉僇僂儞僞偵儘乕僪偟偰丄栠傝傑偡丅

僒僽儖乕僠儞屇傃弌偟偲丄儕僞乕儞偺摦嶌

俛俙俴偱僒僽儖乕僠儞丄俽倀俛傪屇傃弌偡偲丄僒僽儖乕僠儞愭摢偵栠傝斣抧偑彂偐傟丄僾儘僌儔儉偼丄俽倀俛亄侾斣抧偐傜幚峴偟傑偡丅栠傞偲偒偼丄俛丂丆俬丂俽倀俛丂偲偟偰丄俽倀俛偵彂偐傟偨僨乕僞傪傾僪儗僗偲偟偰丄僽儔儞僠偟傑偡丅偙偺傛偆側摦嶌傪偡傞偨傔丄嵞婣屇傃弌偟偲偐丄儅儖僠僞僗僋側偳偱偼巊偊傑偣傫丅

僒僽儖乕僠儞偐傜偺儕僞乕儞柦椷丄俛丂丆俬丂乮僽儔儞僠丒僀儞僟僀儗僋僩乯

僒僽儖乕僠儞偐傜偺儕僞乕儞偼丄栠傝斣抧傪奿擺偟偰偄傞僒僽儖乕僠儞偺愭摢斣抧丄俽倀俛傪丄僀儞僟僀儗僋僩傾僪儗僢僔儞僌偱僽儔儞僠偟傑偡丅僒僽儖乕僠儞乮俽倀俛乯偐傜儕僞乕儞傪幚峴偡傞柦椷偼丄俛丂丆俬丂俽倀俛丂偲彂偒傑偡丅偙傟偱丄俽倀俛偵奿擺偝傟偨抣傪僾儘僌儔儉僇僂儞僞偵儘乕僪偟偰丄栠傝傑偡丅偙偺僽儔儞僠丒僀儞僟僀儗僋僩柦椷偼丄僒僽儖乕僠儞偐傜偺栠傝偩偗偱側偔丄儁乕僕嫬奅傪墇偊偨侾俇價僢僩乮幚嵺偵偼侾俆價僢僩儚乕僪傾僪儗僗乯傾僪儗僗抣偵僽儔儞僠偡傞偲偒偵傕巊偄傑偡丅

弨旛拞

儈僯僐儞偺俫俬俿俙俠侾侽傪丂俽俹俙俼俿俙俶俁偱幚尰丄偦偺俉丂俬俹俴偲丄俷俵俴偺婡擻

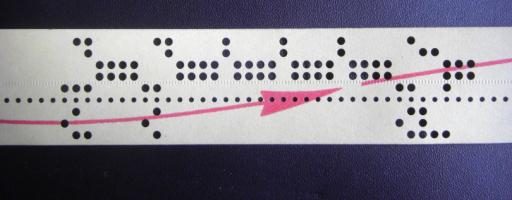

俷俵俴僥乕僾傪撉傒弌偟丄庤摦媡傾僙儞僽儔偱揥奐偟偨傕偺丅

儊儌儕忋偵偼丄愭摢侾斣抧偐傜丄埲壓偺侾俇儚乕僪偺

俬俹俴偑彂偐傟偰偄傞傕偺偲偡傞丅侽斣抧偼幚嵺彂偔昁梫偼柍偄丅

埲壓偼俬俹俴

ADDR DATA LABEL 柦椷 儌乕僪丂傾僪儗僗丄僐儊儞僩

0000 ORG 0

0000 0000 TEMP: DC 0 //儚乕僋僄儕傾

0001 0001 DC 1 //嵟弶偼侾偱丄俷俵俴偺嵟弶傪撉傫偱丄侽侽侾侽偵彂偒姺偊傜傟傞

0002 7024 LOOP: STR

0003 8804 SLL 4

0004 3800 ST TEMP

0005 7021 KTR

0006 4005 B *-1

0007 7032 RTR ,C

0008 880C SLL 12

0009 800C SRL 12

000A 3000 O TEMP

000B 6841 KNC

000C 4002 B LOOP

000D 3C01 ST ,I 1

000E 5001 KCT 1

000F 6842 KZA

0010 4002 B LOOP

0011 // 俷俵俴偺嵟弶偺栺敿暘傪撉傓偲丄僐乕僪侽偲側傝丄

俲倅俙偱丄僗僉僢僾偟偰丄LOOP 偵僽儔儞僠偟側偔側傝

俬俹俴偐傜敳偗弌偰丄俷俵俴偵惂屼偑堏傞巇慻傒偱偁傞丅

嵟弶丄偄偔偮偐偺僼傿乕僪乮俶倀俴俴乯偑昁梫

俷俵俴僥乕僾偺桳岠側乮僼傿乕僪偱側偄乯侽倶俀俋侽僶僀僩撉傓偲丄

俬俹俴偺侽倶侽侽侽俥斣抧偱僗僉僢僾偟偰丄侽倶侽侽侾侾斣抧傊偲恑傒丄

偙偙偐傜俷俵俴偐傜儘乕僪偟偰儊儌儕偵彂偐傟偨侽倶俋俤斣抧偵旘傇丅

埲壓偼俷俵俴偺僥乕僾偺撪梕丅幚嵺偺俷俵俴僥乕僾偼丄

係暥帤偱侾俇價僢僩偺僨乕僞偲側傞傛偆側暲傃偵側偭偰偍傝丄

僼傿乕僪晹暘偑彮偟偁偭偰丄偦偺僨乕僞偑侽偱廔椆偟偰丄

侽倶侾侾斣抧偐傜幚峴偟丄儊儌儕僒僀僘傪僠僃僢僋偟丄

009E --- 00A9 偱僠僃僢僋

晅壛柦椷偺桳柍傪僠僃僢僋偟偰丄

00AC --- 00AE 偱僠僃僢僋

晅壛柦椷婡峔偑側偗傟偽丄僄儈儏儗乕僩晹暘傪捛壛偱儘乕僪偡傞丅

00AD 4020 B 20 俀侽斣抧傊僽儔儞僠偱丄捛壛偺儘乕僪丅

ADDR DATA 柦椷 儌乕僪丂傾僪儗僗丄僐儊儞僩

0000 僼傿乕僪乮俶倀俴俴乯

0000

0000

0000

0000

0000

0010 0010 偙偺侽侽侾侽偼丄侾斣抧偵忋彂偒偝傟傞丅

0011 409E B 9E 11丂弶婜愝掕丄儊儌儕挷嵏偵旘傇

0012 4411 B ,I 11

0013 4072 B 72

0014 0813 L 13

0015 6F00 HLT

0016 4413 B ,I 13

0017 104A A 4A

0018 1017 A 17

0019 205C N 5C 0x2F

001A 3853 ST 53

001B 0811 L 11

001C 8804 SLL 4

001D 3053 O 53

001E 3811 ST 11

001F 4022 B 22

0020 8000 SRL 10 20斣抧

0021 3800 ST 0 侽斣抧僋儕傾

0022 4849 BAL 49 撉傒庢傝儖乕僾愭摢偐丠

6842 KZA

4028 B 28

0025 4849 BAL 49 侽側傜孞傝曉偡

6842 KZA

4025 B 25

0028 6866 KPA,KNA

4022 B 22 儅僀僫僗

1867 S 67 0x1C 傪堷偔

6846 KMA,KZA

4022 B 22

1866 S 66 0xFFEF

6864 KPA

4018 B 18

0030 185B S 5B 30斣抧 0x6

6864 KPA

4022 B 22

0033 6862 KNA

4089 B 89

1A5B S 5B 0x6

6866 KPA,KNA

4017 B 17

8802 SLL 2

1068 A 68 0x4055 B 55

383C ST 3C

0811 L 11

003C 0001 ? 僒僽儖乕僠儞愭摢

003D 3853 ST 53

003E 8801 SLL 1

003F 6862 KNA

0040 4044 B 44 40斣抧

0041 6861 KZC

0042 2820 X 20 0x8000

0043 403E B 3E

0044 0853 L 53

0045 6841 KNC carry==1

0046 503C KCT 3C 栠傝斣抧亄侾

0047 443C B ,I 3C

0048 7EFF ? address

0049 0001 ? 僒僽儖乕僠儞愭摢

004A 0805 L 5 KTR 7021丂偙偙偼丄俬俹俴偺柦椷偐傜僐僺乕

004B 3851 ST 51

004C 0802 L 2 STR 7025丂偙偙偼丄俬俹俴偺柦椷偐傜僐僺乕

004D 3850 ST 50

004E 0807 L 7 RTR ,C 7032丂偙偙偼丄俬俹俴偺柦椷偐傜僐僺乕

004F 3853 ST 53

0050 0001 ? STR

0001 ? KTR

0052 4051 B 51

0053 0001 ? RTR ,C

483C BAL 3C

0055 6F00 HLT

2060 N 60 0x7F

185C S 5C 0x2F

4449 B ,I 49

3848 ST 48 index 4 1

4022 B 22

0006 ?

005C 002F ?

8810 SLL 10 index 8 2

6F00 HLT

4411 B ,I 11

0060 007F ? 60斣抧

1800 S 0 index 0xc 3

6842 KZA

6F00 HLT

4020 B 20

4411 B ,I 11 index 0x10 4

FFEF ?

0067 001C ?

0068 4055 B 55

8810 SLL 10 index 0x14 5

1811 S 11

3811 ST 11

8810 SLL 10

006D 3C48 S ,I 48

5048 KCT 48

5011 KCT 11

406D B 6D 70斣抧

4022 B 22

0072 3898 ST 98 妱傝崬傒張棟丠丠

088F L 8F 晅壛柦椷桳傝偱丄侽倶俉侽侽侽丄柍偟侽倶俈俥俥俥

0074 6864 KPA

F099 STE 99 ?

0076 6900 LCAR

3897 ST 97

0078 68E8 KPEC,R

4C90 BAL ,I 90

007A 68E4 KMEC,R

4C91 BAL ,I 91

007C 4C92 BAL ,I 92

007D 68E2 KAEC,R

007E 4C93 BAL ,I 93

007F 68E1 KOEC,R

0080 4C94 BAL ,I 94 80斣抧

0081 0897 L 97

6A00 SCAR

088F L 8F

6864 KPA

C099 LE 99

0898 L 98

6C00 SIM

0088 4400 B ,I 0

0811 L 11

3C48 ST ,I 48

1000 A 0

3800 ST 0

5048 KCT 48

4022 B 33

008F 7FFF ?

0013 ? 90斣抧

0013 ?

0011 ?

0013 ?

0094 7EFF ? --->0013

0202 ?

0096 7EFF ?

1000 A 0 ? 俠俙俼俼倄戅旔

0098 0100 ? 俙俠戅旔

0013 ?

0001 ?

0001 ?

0001 ?

0001 ?

009E 0813 L 13 code B 72丅俷俵俴偺嵟弶偵幚峴偝傟傞応強丅

俷俵俴傪侽倶俀俋俀撉傫偩偁偲丄偙偙偵棃傞丅

3801 ST 1

00A0 0C96 L ,I 96 address is 0x7EFF

68C2 KAEC 偙偙偱丄儊儌儕偺幚憰偺忋尷傪挷嵏

40A9 B A9

0896 L 96

00A4 1897 S 97 0x1000丂係俲儚乕僪扨埵偱壓偘傞

3896 ST 96

00A6 3848 ST 48

3894 ST 94

00A8 40A0 B A0

00A9 5048 KCT 48

5094 KCT 94

C898 LD 98

00AC 68E1 KOEC,R 偙偙偱丄晅壛柦椷婡峔偺桳柍傪僠僃僢僋

00AD 4020 B 20

00AE 1096 A 96 0x100

00AF 3896 ST 96 result is 0x1FFF

00B0 F094 STE 94 B0斣抧

00B1 508F KCT 8F

00B2 6F00 HLT

00B3 4020 B 20

0000

0000

0000

僥乕僾偼偙偙偱丄僼傿乕僪偲側傞乮俶倀俴俴乯

偦偺屻丄埲壓偺傾僗僉乕暥帤僐乕僪偑懕偔丅

埲壓偼僾儘僌儔儉偩偑丄儘乕僪偝傟傞傾僪儗僗偼丄

巊偆俫俬俿俙俠侾侽偵幚憰偝傟偰偄傞儊儌儕偺

嵟屻偺侽倶侾侽侽儚乕僪偺愭摢偐傜偝傟傞丅

倃俬俴俬俶倃偺僄儈儏儗乕僞-偱偼丄儊儌儕傪

係俲岅幚憰偟偰偄傞偺偱丄

儊儌儕僠僃僢僋偱僄儔乕偱

0x0F00丂儚乕僪傾僪儗僗偐傜儘乕僪偝傟傞丅

幚僶僀僩傾僪儗僗偼丄侽倶侾俤侽侽斣抧丅

埲壓偺僾儘僌儔儉偼丄晅壛柦椷偺僜僼僩僄儈儏儗乕僩

偱偁傞丅

0000@0800@1B2E@3B31@0F31@3B30@2334@3B32@

0B30@8806@6844@431D@0B31@2333@3332@3B2F@

6861@0F2F@3B2F@0B30@6864@4319@800B@132C@

431B@800B@131F@3B1C@

0001K

8010@430E@430C@4371@4381@4376@4386@4340@

433D@4343@4352@43BE@43DC@436B@4368@432D@

43F6@0001@

0001K

0001K

0001K

0001K

FE00@01FF@000F@0010@8000@43F6@436E@7FFF@

0001K

43F6@0F2F@3898@532F@0F2F@3899@4700@0F2F@

3B30@532F@0F2F@1099@3899@6900@1330@6861@

4365@1098@3898@6900@3897@4700@0F2F@3B30@

532F@0899@1F2F@3899@0898@6861@435D@1B30@

434E@1B2E@6841@435B@1B30@3898@0B2E@3897@

4700@1098@3898@4362@0898@3F2F@532F@0899@

3F2F@4700@0B2F@3899@4700@4B9B@4BB2@532F@

4372@4700@4B9B@0898@2337@3B31@4BB2@3331@

3898@532F@437A@8810@4363@4B9B@4BA5@532F@

4382@4700@8010@3B32@4B9B@0898@2337@3B31@

4BA5@0898@2B31@3332@3B32@532F@438C@0B32@

800F@3897@0898@233A@3331@3898@4700@0000@

0B2F@2335@3B2F@6862@1B36@1B2F@1B2F@3B2F@

479B@0000@0899@8801@3899@6900@3B30@0898@

8801@3330@3898@6900@3897@47A5@0000@0898@

880F@3B30@0899@8001@3330@3899@0898@8001@

3898@47B2@8810@3897@3898@0BFA@3BFB@0F2F@

3B2F@6A00@8001@3B2F@0898@6861@1099@3898@

6900@880F@3B3B@0898@880F@132F@3B2F@0898@

8001@133B@3898@0B2F@53FB@43C5@3899@4700@

0898@1F2F@6841@43F3@0BFA@3BFB@4BA5@0898@

1F2F@6841@43EC@3B32@0897@6862@43EE@0B32@

3898@5099@53FB@43E2@8810@3897@4700@0B2E@

3897@4700@0BF9@3813@4014@0081@FFF0@0000@

CCC0I

0300H

媡傾僙儞僽儖乮堦晹乯僄儈儏儗乕僞偱偼丄侽倶俥侽侽斣抧偐傜

儘乕僪偝傟偰偄傞丅

0100 0000

0101 0800 L 0

0102 1B2E S 12E

0103 3B31 ST 131

0104 0F31 L ,I 131

0105 3B30 ST 130

0106 2334 N 134 // 01FF

0107 3B32 ST 132

0108 0B30 L 130

0109 8806 SLL 6

010A 6844 KMA // ,I

010B 431D B 11D

010C 0B31 L 131

010D 2333 N 133 // FE00

010E 3332 O 132

010F 3B2F ST 12F

0110 6861 KZC

0111 0F2F L ,I 12F

0112 3B2F ST 12F

0113 0B30 L 130

0114 6864 KPA

0115 4319 B 119

0116 800B SRL B

0117 132C A 12C

0118 431B B 11B

0119 800B SRL B

011A 131F A 11F

011B 3B1C ST 11C

011C 0000

011D 8010 L 10

011E 430E B 10E

011F 430C B 10C

0120 4371 B 171

0121 4381 B 181

0122 4376 B 176

0123 4486 B 186

0124 4340 B 140

0125 433D B 13D

0126 4343 B 143

0127 4352 B 152

0128 43BE B 1BE

0129 43DC B 1DC

012A 436B B 16B

012B 4368 B 168

012C 432D B 12D

012D 43F6 B 1F6

012E 0001

012F 0000

0130 0000

0131 0000

0132 0000

0133 FE00

0134 01FF

0135 000F

0136 0010

0137 8000

俷俵俴巻僥乕僾偺僶僀僫儕乕僀儊乕僕偱偡丅巒傔偲廔傢傝偵抁偄僼傿乕僪晹暘偑偁傝傑偡丅俷俵俴僥乕僾

俵俙俽俽僥乕僾

俷俵俴亄俵俙俽俽偺俽儗僐乕僪僼傽僀儖

S3150041000000000000000000000000000000000000A9 OML--->

S3150041001001100400091E040401110400071200081E

S315004100200113060F0010040401130100041A010014

S3150041003001170200051C03080513000801110808F1

S3150041004000140300051303080111040002120800FD

S3150041005000100308001004080419060804120400DD

S3150041006002180408041906080412040002150608B9

S3150041007006160400021201080617060804160400B3

S3150041008002120108061606080614040001180108A2

S31500410090051B06080614040002120608061204008F

S315004100A00819010A051B0608061604000117080867

S315004100B00012010006180308031C00080111000084

S315004100C0001103080513080800110608061204006A

S315004100D0041406080611020802100400031E000853

S315004100E00513060804110500031C0404031C070E2E

S315004100F00F1F000000110008001503080511000834

S315004101000012030805100008001703080513000034

S31500410110001100000011040005110000001104083F

S31500410120031C060F0010020006100108051C0404FA

S315004101300419030804180400021200000016000006

S31500410140021F08080110060F0010040401110000E7

S31500410150071F0108001006080412060F00100400CC

S315004101600210040401110F0F0E1F0000011C0400B0

S3150041017005150808011001080111030801110808B5

S315004101800110030C041805000418050001110400B0

S31500410190061D04000212030809180008081F060874

S315004101A006140F0009190609001003080917060865

S315004101B00E18040C091006080E14040C0911040C3F

S315004101C0091206080E12040C091306080E11040C36

S315004101D0091400080917060A00100008081F060836

S315004101E006140C00091900080918060C001004042D

S315004101F0001000080111030C041801000010030847

S3150041020000100500041804000212070F0F1F00001A

S315004102100113000001130000011100000113070E34

S315004102200F1F00020012070E0F1F010000100001F0

S315004102300010000001130000001100000011000031

S315004102400011000000110008011303080011000C01

S31500410250091606080C1204000A19000809160108B5

S3150041026009170308091603080418030809140400AA

S315004102700A1005000418050009140C080918060897

S315004102800E110400021001000916030809160F0099

S3150041029009140500081F060F001004000210000093

S315004102A000100000000000000000000000000000F7

S315004102B03030303040303830304031423245403392 偙偙偐傜晅壛柦椷僄儈儏儗乕僞

S315004102C0423331403046333140334233304032336A

S315004102D033344033423332400D0A304233304038B2

S315004102E03830364036383434403433314440304245

S315004102F03331403233333340333333324033423256

S3150041030046400D0A36383631403046324640334251

S315004103103246403042333040363836344034333119

S315004103203940383030424031333243400D0A34335C

S3150041033031424038303042403133314640334231E8

S3150041034043400D0A303030314B0D0A3830313040A0

S3150041035034333045403433304340343337314034DD

S3150041036033383140343337364034333836403433DA

S315004103703430400D0A34333344403433343340341B

S315004103803335324034334245403433444340343389

S31500410390364240343336384034333244400D0A34E1

S315004103A03346364030303031400D0A303030314BF3

S315004103B00D0A303030314B0D0A303030314B0D0A99

S315004103C0303030314B0D0A464530304030314646AB

S315004103D04030303046403030313040383030304077

S315004103E03433463640343336454037464646400D2B

S315004103F00A303030314B0D0A3433463640304632BE

S3150041040046403338393840353332464030463246F5

S3150041041040333839394034373030403046324640FF

S315004104200D0A334233304035333246403046324648

S3150041043040313039394033383939403639303040F6

S31500410440313333304036383631400D0A3433363560

S3150041045040313039384033383938403639303040D8

S3150041046033383937403437303040304632464033BE

S31500410470423330400D0A35333246403038393940FF

S31500410480314632464033383939403038393840368A

S3150041049038363140343335444031423330400D0AE9

S315004104A03433344540314232454036383431403474

S315004104B03335424031423330403338393840304267

S315004104C032454033383937400D0A343730304031C0

S315004104D03039384033383938403433363240303861

S315004104E03938403346324640353332464030383922

S315004104F039400D0A33463246403437303040304277

S315004105003246403338393940343730304034423915

S315004105104240344242324035333246400D0A34334A

S3150041052037324034373030403442394240303839FE

S3150041053038403233333740334233314034424232EA

S315004105404033333331400D0A33383938403533324D

S3150041055046403433374140383831304034333633CE

S315004105604034423942403442413540353332464087

S315004105700D0A343338324034373030403830313038

S315004105804033423332403442394240303839384080

S31500410590323333374033423331400D0A34424135E9

S315004105A04030383938403242333140333333324088

S315004105B03342333240353332464034333843403068

S315004105C0423332400D0A38303046403338393740AD

S315004105D03038393840323333414033333331403365

S315004105E038393840343730304030303030400D0AB9

S315004105F0304232464032333335403342324640361A

S315004106003836324031423336403142324640314209

S3150041061032464033423246400D0A34373942403041

S31500410620303030403038393940383830314033381D

S3150041063039394036393030403342333040303839F9

S3150041064038400D0A3838303140333333304033384F

S3150041065039384036393030403338393740343741CC

S315004106603540303030304030383938400D0A38382E

S3150041067030464033423330403038393940383030B3

S3150041068031403333333040333839394030383938B3

S315004106904038303031400D0A3338393840343742EA

S315004106A03240383831304033383937403338393889

S315004106B0403042464140334246424030463246400F

S315004106C00D0A3342324640364130304038303031BF

S315004106D04033423246403038393840363836314038

S315004106E0313039394033383938400D0A36393030AE

S315004106F0403838304640334233424030383938400A

S315004107003838304640313332464033423246403003

S31500410710383938400D0A3830303140313333424070

S3150041072033383938403042324640353346424034D8

S3150041073033433540333839394034373030400D0A48

S3150041074030383938403146324640363834314034D3

S31500410750334633403042464140334246424034427A

S3150041076041354030383938400D0A314632464036F7

S3150041077038343140343345434033423332403038A4

S315004107803937403638363240343345454030423386

S3150041079032400D0A333839384035303939403533EE

S315004107A04642403433453240383831304033383967

S315004107B03740343730304030423245400D0A3338C5

S315004107C0393740343730304030424639403338315A

S315004107D0334034303134403030383140464646304B

S315004107E04030303030400D0A43434330490D0A30E2

S315004107F033303048000000000000000000000000D7 <---OML end

S3150041080000000000000000000000000000000000A1 MASS --->

S3150041081000000030303941478D0A30303030C03029

S31500410820303030C030303030C030303030C08D0A9A

S3150041083030303030C98D0A0000000000000030B170

S31500410840B830478D0A30423939C0B83030B1C0B1BD

S31500410850303936C033B8B4B8C0B4424435C0334237

S315004108603941C0B4424244C041303036C08D0AB4E9

S31500410870424244C041303036C0B4424244C0413065

S3150041088030B4C0C6334244C041B830B1C0B8B83004

S3150041089033C0413030B1C08D0AB13339C5C033425E

S315004108A03933C030424244C08D0A303030B14B8D6D

S315004108B00AB233C6C6C0B130B439C0B4B73933C091

S315004108C0C630B4B8C0B433B836C030B23030C08D9B

S315004108D00A303030B14B8D0AB8B8B130C036C63067

S315004108E030C0B43339C6C0B4333933C0C6333933B3

S315004108F0C036443030C0B4B73933C030303941C026

S315004109008D0AB8303030C0B1424244C033B8353375

S31500410910C0B4424435C033C3B4B8C03530B4B8C0EE

S31500410920B4334230C030B1B830C08D0AB1423941DA

S31500410930C036B8B4B2C036C63030C0B433B8B4C06D

S31500410940B4334142C035303533C0B4334136C0B4D7

S3150041095033B836C08D0AB43342B7C030423939C094

S31500410960B130B439C0B433C5B4C0B4424435C03033

S31500410970424244C033C3B4B8C03530B4B8C08D0A5E

S31500410980B1333941C0B433B835C08D0A303030B196

S315004109904B8D0A36443030C0B4B8B439C036B8B4D9

S315004109A0B2C0B433C336C0B4B8B439C036B8B4B281

S315004109B0C0B433C3B2C0B43342C6C08D0AB13035B8

S315004109C0C3C036C336B2C0B43342C5C0B4B742441D

S315004109D0C08D0A303030B14B8D0A41303044C0B100

S315004109E03341B2C033423933C041B830B4C033B8B1

S315004109F03530C030424133C0B8B43530C036B83630

S31500410A00B2C08D0A30424133C0B4B7C341C08D0A2A

S31500410A10303030B14B8D0A30B8B4B8C0B2424141E2

S31500410A20C0B8B830B8C036C33635C0B433C644C0D2

S31500410A3030B8B4B8C0B442C341C033B73933C08DFE

S31500410A400A33C63933C030B8B4B8C0B2424141C0E6

S31500410A50B83030B7C036B8B4B2C0B433C644C033C8

S31500410A60B8B439C0B1B83936C08D0A36B8B4B4C095

S31500410A7036C63030C0B1303936C0B442C341C0B297

S31500410A80B73933C036B8B4B2C0B43342B4C0304219

S31500410A904141C08D0A33B83530C0B4423933C033D1

S31500410AA0424141C033B835B1C030C33530C033C3DC

S31500410AB035B1C035303530C0353035B1C08D0A30ED

S31500410AC0B83530C0B8B830B7C036B8B4B2C0B433F0

S31500410AD0C6B2C030424435C0B4423933C033424411

S31500410AE035C0B8B8B130C08D0AB4B74435C030B19D

S31500410AF0C6C6C08D0AB73342B2C98D0A30B1B830C5

S31500410B00CA000000000000000000000000F042881A

S31500410B1041C0A041C0A04266C0716AC0716AC0713D

S31500410B206AC0C0C0C0C044C041C0A041C0A041C00D

S31500410B30A056E2C05FC34178E2C3E4C341F9E2C3D0

S31500410B405CE2C36363C0CAE7C3DBE2C3CFE2C0E48E

S31500410B50E1C665C344E163C0FF66C3E263C0C9E75A

S31500410B60C36063C07E66C3C977C044E1C6534B4484

S31500410B70CA77C077E241CA77C3CA47C5FFC6C5D758

S31500410B804B4465C3447EC6C5DB4B44C947C54B4B45

S31500410B9044C977C0416048C977C34EC34441C0C0C8

S31500410BA0F0FFCFFF7ECF72C3C077C3C0C0FFCFE493

S31500410BB063C0C9E7C3DB72C05C72C3DB42C55C423A

S31500410BC0C5C947C5E7C34477E4C071F3C377E44178

S31500410BD0FF4744D2CCC06F53C5FF7B4E7B6FC6C027

S31500410BE0C0C0C0C048C0C0C0F06FC3C0E4C6716FCA

S31500410BF0C3FAE2C0726FC3F9E24144E1C6C05F4441

S31500410C0072FFC0C06F41E2E1C650CF44726FC0F37C

S31500410C10CF41C5CF4472CFC572FFC0656FC3C660B1

S31500410C204872CFC572FFC0776FC341E1C6DBCF447F

S31500410C3077FFC0776FC3656FC0F6CFC3656FC37467

S31500410C40CF42F56F41E2E1C669CF44716FC0C0E85A

S31500410C50C6F06FC0C0C0C0C05F44C0CFC5C05F440E

S31500410C60C06FC077FFC377CFC5716FC0C0E8C6F00C

S31500410C706FC0775F44C0C0C0C0C0C0C0C0C0C3C0A1

S31500410C80C0C060CFC06044C050C0C0C0C0C0C0C0BA

S31500410C90C0C0C0C0C0C0C0C0C0C0C0C0C0C0C0C00D

S31500410CA0C0C0C0C0C077CFC047C0A0E8C0A041C047

S31500410CB0A07DC0A041C0A041C0A041C0A041C0A0EC

S31500410CC041C0A041C0A041C0A041C0A041C0A04177

S31500410CD0C0A041C0A041C0A041C0A041C0A041C0E8

S31500410CE0A042C0A041C0A041C0A041C0A041C0A0F7

S31500410CF041C0A041C0A041C0A041C0A041C0A04147

S31500410D00C0A041C0A041C0A041C0A041C0A041C0B7

S31500410D10A042C0A041C0A041C0A041C0A041C0A0C6

S31500410D2041C0A041C0A041C0A041C0A041C0A04116

S31500410D30C0A041C0A041C0A041C0A041C0A041C087

S31500410D40A041C0A041C0A041C0A041C0A041C0A097

S31500410D5041C0A041C0A041C0A041C0A041C0A041E6

S31500410D60C0A0C3C0A041C0A041C0A0604EB7FF47CC

S31500410D7088C0FCC6C0FC36C04888C0F0C6F9E2C08F

S31500410D80F966C3FA66C3F3E2C0E1E7C3F5E2CCE232

S31500410D90E7CFC06CC6C3C048CF60485FE2C341607D

S31500410DA048DBCACCD2E7CF50FA44D247C5C0F0C6D9

S31500410DB0F3E2C0E147CCC9E7CFF342CFF5E2C0DB6E

S31500410DC0E2C3E2E7CCF5E2CF566C44DE6AC0786610

S31500410DD0C3F9E2C07B66C34D6ACCEE66CFFC66CFF3

S31500410DE05FE7CFEB66CFDBCACCD4FA44E84844EDA3

S31500410DF04844C06CC6426048E1E1C66C4844F0488C

S31500410E0044C06CC6E4E1C678CFC65347CFCFFA4457

S31500410E1050FA4459CACC506F446F66C0C0E8C64DBB

S31500410E206ACCE866CFF066CFDBE7CF6C66CFE1E10F

S31500410E30C6EE66CF6047C5D1FA44E1FC44FF47C0E0

S31500410E40D2FA44C0C944FF484444CA4459C94453E8

S31500410E50FA44FFC944D4FA444DC94459C94459C90D

S31500410E6044F966CC55FA44C9CA44D877C044E1C668

S31500410E70C6CA4444CF42D877C3D847C5D847C5D751

S31500410E80E7C0D877C353FA44FFC94472E2CC55FA56

S31500410E90447DC944D877C0D847C5D847C54160487D

S31500410EA04EC048E2E1C6EBC94441C04842E1C6D81A

S31500410EB05A44D877C0D8E7C3D8D744E1E1C6F5C983

S31500410EC04450C048DDE7C3EB66C0E2E1C65FCA44B1

S31500410ED0CCFA44C060C65FCA44C36FC0DDE7C3EB0A

S31500410EE066C042E1C65FCA44CCFA445572445FCA01

S31500410EF044DD6AC056FA447166C0D7FA44C055C04B

S31500410F00D747C5F548445AFA44F548445C6AC05641

S31500410F10FA4459C94459FA44C0C0C059C944F06059

S31500410F20C0C0C0C0C0C0C0CCE4C0CC63C06A53C05E

S31500410F30655FC0F6DDC0ED65C0DBE4C0F3E2C07DB0

S31500410F4060C05953C0C060C0D1D7C0FA5FC0F34832

S31500410F50C37248C37B42C0D877C071C6C37166C3EA

S31500410F60E2FC4459C9444EFC44DBE7C042E1C6FFBA

S31500410F70C944F366C0F9E24141E1C6F3CA44F366A6

S31500410F80C04EED41E1E1C6CC4B44F066C0E2E1C65C

S31500410F90F5CA44506CC056FA44F366C0C9C048729B

S31500410FA066C3D7E7C0C9C04872664142E1C64E4BE7

S31500410FB044F366C041C9424E4DC371C6C37166C34F

S31500410FC0F36941E2E1C6CA4B447166C07B6941425D

S31500410FD0E1C6FFC944C36FC0EB66C3FFC944F366AC

S31500410FE0C0C04B447166C0C56048E4E1C6EB4B44A2

S31500410FF0DE6AC0D8E7C3786641E2E1C6E24B44D82F

S3150041100077C0F3664142E1C65F4B44D8E7C071C63B

S31500411010C3D4CCC3C0CA44D847C5D8E7C0D44B44CF

S315004110207866C077E241E2E1C6EB4B44F366C078AD

S31500411030F6C37866C078C6C55C4B44FA66C07B6623

S315004110404142E1C6FA4B44F966C0C9E7C3536C4114

S31500411050F966C3CAE7C3CFFC44FA66C0DBE2C353B1

S315004110606C41FA66C3566C447B66C0536C417B66E1

S31500411070C37D664166E1C655FC447B66C0C36F418C

S31500411080C9E7C3D7E7C0C36F417BF6C37166C0D218

S31500411090CCC3C977C3C947C5F366C0C977C3D16C49

S315004110A0C0C0CA446CDBC0C6E4C072D4C3F9724442

S315004110B041C0A0C3C0C0C050C0DB65C041C0A0DBB9

S315004110C0E2C0C9E741E2E1C6565C44C977C0CA7786

S315004110D0C3C947C5CA47C5D7CC44E4D7C0C05FC01A

S315004110E0F9D7C041FF446CC6C54EFC44D4FA44E12D

S315004110F04D4469CC4444E7C060ED41DE4DCC42E10C

S31500411100C65F4DCCD14DCF7B66C0FAE2C3F9E24111

S31500411110E2E1C6C54D447BC6CC78E2C0DBE2CF50A6

S315004111206F445C72C0D7FA44C055C0D747C55C42CC

S31500411130C5DBE2C05CE24142E1C678CC44DBE2C0B9

S31500411140786641E2E1C6484D44F942C67866C0F642

S31500411150CC445F42C6506F445FE2C0D7FA44C055A3

S31500411160C069C6C5C048C0F366C0D7FA4441C0A0ED

S31500411170CFFA44F9C6CC7B66C0C3CF41F0E2CFC0BB

S3150041118074C6C0FCC6D2E7C0536C41E2E1C6D74D36

S3150041119044504844CAC9C048C5C07BC0C0F966C0AE

S315004111A041E7C37B6641E2E1C6D74D447B66C0FF5A

S315004111B066C3F966C07E66C353CC41C0E7C3FF66CA

S315004111C041E2E1C6CF4E447EF6CC47E7CF44CF421B

S315004111D0C5E7CFC077CC44CF42C5E74D44E1C66AA7

S315004111E04E44C077CC7EF6CF47E7CCC077CF7EC69C

S315004111F0C57EC6C5C047C5C047C57EF6C0C5E7C39F

S31500411200C077C07EF6C3C5E7C0C077C37EC6C5C03A

S3150041121047C5C0E7C0FF664142E1C66F4D44FF6620

S31500411220C0536C41E74D444177CC4147C54147C521

S31500411230E4E1C6664E44F3EECFC06CC64D6048E469

S31500411240E1C6604E4441D7CCC0FF44F64EC06FEE76

S31500411250CCFF7E445F47C542FF444147C541E7C095

S315004112607B664142E1C6CF4E44D74D4444CF42F915

S31500411270EECF71EECCDD4E447EC6C57EC6C5C047B7

S31500411280C5C047C5C64E44F34EC074FFCFF94EC0E4

S3150041129074FFCF42C0A060C04242C0A0CA74C042DF

S315004112A0C0A060C0424E55C5C6D144CA74C065632C

S315004112B0C06C63C0F665C05AE2C0FFFFCFFFFF476F

S315004112C041FF44C0C0C674E2C0F3E2C3E1E7C3F5DF

S315004112D0E2CFE2E7CF44CA4441FF44C0FCC644CA18

S315004112E04441C0A0D747CFC36FC06966C36CC6C56A

S315004112F0D7E7C0D7FA44474DC0505F44D4FA44DDDE

S31500411300CF44F5484444CA4453FA44F54844F9663F

S31500411310CC55FA44F0CF44D877CC44E1C6F3CF4418

S3150041132044CF42D877CFD8E7C0F6CF4147E7C3602D

S31500411330FC44E1FC44EDCF4477FF444777C3F5488D

S315004113404459FA44C0C0485FCF445C6AC056FA4427

S31500411350F5484442C0C0CF65C041C0A04441474161

S315004113604147FACF44424147785F44F0C3BBC0503E

S315004113708850FF44C6FF44FA4E4472E2CC4DFF44C6

S31500411380474844F94D4447FF44C0C04850C048CF40

S31500411390E7C3F6E2C04D77C3F342414DE7C34EE79B

S315004113A0C3E8EB41F5E2C3F66A44E865C04D77C34D

S315004113B048FF44D16F446047C56AEB44CAFF44CAFB

S315004113C0C0C0636941E2E1C6CAFF44C060C6C9FF05

S315004113D044594844D84844564844EB4844776944BC

S315004113E0C9FF44CFC944CFC944CFC944EB4844E4BB

S315004113F0484444E7C0666944CAFF44CFC944E46FE0

S315004114004466694465F944744844F04844E1694195

S3150041141042E1C6F9484444E7C0666944E46F44E49E

S31500411420694142E1C67E4844EB4844C9FF44CFC9BD

S3150041143044CFC944CFC944CFC94444E7C0E2694116

S31500411440E2E1C6CFC944D86F444BC9447769447E6B

S315004114504844666944CAFF44CFC9447E4844E46F60

S3150041146044E2694142E1C65CC944666944E16CC0F3

S315004114706669445AE8C0666944F5E2C0F3E241F65A

S31500411480E2C3FA4E44E16CC06669445AE8C06669F3

S315004114904456484460C0C07EC0C0FCC0C06CC0C099

S315004114A078DEC041C0A047E7C3CFE7C0C0E8C64128

S315004114B0E1C671C94447E7C04ED7C34E77C3CF474C

S315004114C0C56659444E47C5F542C548FF4447E7C03E

S315004114D0486048EEC94441C0A0C6FF447759444DCF

S315004114E077C0E2E1C6D1CA44EB6ACCE765CFE7F5FE

S315004114F0CC74664DE2E1C65060CA42E1C6CACA44EE

S31500411500E8EDC0666944E865C0666944775944E8D0

S31500411510C5C5E7C5C5E7C5C54D77C0E8654142E1E3

S31500411520C6FFC94474C6CCED6A44ED6A44F5C6CCDF

S31500411530ED6A44ED6A4477594474C6CCED6A444435

S31500411540E7C066694465F9445FCA44DBCA446669D3

S315004115504444E7C05AE841E2E1C6E7CA44CAFF4407

S31500411560CFC944775944D16F446047C56AEB44E4D7

S31500411570CA4469C5C0C0C0C041C0A050C048486047

S31500411580CAE16941E2E1C6775944E1C94166694424

S31500411590ED5A4441C0A0EB6ACCE765CFE46F4455B0

S315004115A0EB41E2E1C6CAFF44F65A44E46F44D86FC0

S315004115B044504B44C6FF447ECA44E865C0D7EB411C

S315004115C044E1C64D4B44E8C5C57466CCE7F5CFE763

S315004115D0C5C5E7C5C57ECA44D8EBC04BFF44F65ADC

S315004115E04456EB41E2E1C6F65A4469EBC04E4B44E0

S315004115F0E8C0C069C0C0DEC0C072CCC350FF44EE73

S31500411600C6C5D877C0F342414DE7C3C0C0C6E8EB73

S315004116104150E7CFF66A44E865C04D7741E2E1C6FD

S31500411620FA4E4469EBC0FA4D44FFFFCF71D4C34132

S31500411630C0A05F6CCC42E7CFEE66C042E1C64DCC5E

S31500411640444DED447E6C4444E7C05AE84142E1C60C

S31500411650ED4B44E4E7C342E7415FCC4160CCCC4229

S31500411660E7CF6ADB4444E7C05AE841E2E1C6F64BBC

S3150041167044EE66C0E2E1C64BCC44726C44E8ED41AF

S3150041168042E1C6C9CC44726C44726C44EB6C44FC76

S315004116904B444DED44FC4B44726C44E8ED41E2E170

S315004116A0C653CC44EB6C44714B44726C4441604824

S315004116B0EBCA41E765C3E755CCE26C44E26C44E7CB

S315004116C0C5C5E755CCE26C44E26C444DCC44F07E52

S315004116D0CFFF44C04DC0C041C0A050C0484860CAB9

S315004116E044E7C3E16941E2E1C64DCC447E6C44E244

S315004116F05C4441C0A044E7C042E1C6EB5C446FC6CE

S31500411700C5726C44EB5C4441C0A0D1E7C0C0E8C699

S315004117105077C041E1C6FACC444860485047C54875

S31500411720C04844E7C3D147C5725C4441C0A042E7C3

S31500411730C0C0E8C644E7C041E1C6CA4D44C3D7C3A9

S31500411740C377C3C347C54247C57E5C44FC4B444847

S315004117506048C377C3474D4441C0A04260C0C5C03D

S31500411760CCD4EDCF4760C0D7EDC3C074C641C0A04D

S3150041177041C0A0554D4441C0A0C0F0C6FC60446381

S315004117804D44E84D4244E7C3E2E1C64E4D44E8EDDF

S3150041179041E2E1C64E4D444DDD44E7EDC04BFF44C9

S315004117A0C0FCC64E4D4471C0C3FF41C0E8EBC0E822

S315004117B066C3CCFF447266C0C5FF44C055C0D74717

S315004117C0C5E8EBC06966C3F366C0CF5F44C6FF4454

S315004117D0FA4E4472E2CC4DFF44FC4D4447EEC04BB9

S315004117E0FF44FA4E4447FF44C0C0C05047C5504726

S315004117F0C55047C5E46F44CAFF44444E44487E44FD

S315004118004D77C3FA4E447448C3CF65C050FF445028

S31500411810C048FF66C3E46F44426F4142E1C6FF4E92

S3150041182044CAFF44744E44426F41E2E1C66F4E449E

S31500411830FF66C0C0E8C644E7C041E1C66C4E44718C

S31500411840C6C3C5FF44C055C0E8EBC06966C3D747A8

S31500411850C5FFC6C544E7C05AE84142E1C6504E44B9

S315004118606966C042E1C669C6C5D16F446047C56A6B

S31500411870EB44504E444860487166C3604E44CAFFCB

S3150041188044744E44426F41E2E1C6554E44FF66C040

S31500411890C0E8C6E1E1C6FC4E446966C0E2E1C6D194

S315004118A06F444E5F447166C0E1C9C3CF5F44C36FA5

S315004118B0C04BFF44504E44E2C0C0F044C3ED65C046

S315004118C07D60C0F6DDC04E60C0C6E4C0655FC0C085

S315004118D05FC0F3E2C06CDBC0DBE4C0F548C0C0CA00

S315004118E0C0F665C041C0A044FF44D15F44D15F44C6

S315004118F0C5FF44C0C0C0D15F4441C0A044E7C0E277

S315004119006F41E4E1C660CF44636F4166E1C6D8CF1B

S31500411910C544E7C0D85F444141C059C0C041C0A099

S3150041192044E7C0E16941E2E1C6CAFF44EBCF446600

S31500411930CF4444E7C0E45F44F96F44F3CF44CCFF5E

S3150041194044F366C071C6C3CF5F4448E8C071C6C39D

S315004119507166C3CAFF446FCF446FCF4441C0A0E410

S315004119606F44E46941E2E1C6CAFF44F9CFC5F95F74

S315004119704444F936C0D888E7EBC05AE2C3DDE2C336

S31500411980D8FF44666A44D7C944D46F4144E1C6CFBF

S31500411990CA44DBE2C0E2E1C65CE2C042E1C6CF48EE

S315004119A044D7C9446566C0E766C3E7EBC0C0E741B3

S315004119B0DEE7C35FC0C65A42CFD76A44DBE2CC4EAC

S315004119C0E7CF44E7C0536A41E2E1C6C06F446A4883

S315004119D044666A4460484456CA4144E1C6CFCA4453

S315004119E05CE2C065C6C5E84844E7EBC05CE241DE5F

S315004119F04741DEE7C34EE7CCDBE2CFDEE7C0E2E1BB

S31500411A00C644C94444E1C6F3C9445CE2CC41C0CAB8

S31500411A10DD42CFDBE2CC41C0CAD8EB4EDB42CFDD63

S31500411A2042CCD8EB4E5C42CFE74BCCD8EB4EDD42B5

S31500411A30CF5AE2C056CA415AE2C3D76A44DE47C5C5

S31500411A40714844DDE2C044E1C650C94450C04841F2

S31500411A50C0C6DB424D44E1C6CFC9445A42C5C06007

S31500411A60C641C0CADBE2CFE7C6C5D7C944E7EBCC1E

S31500411A70DDE2C3DBE24DDBE2CFD76A445FE2C0423F

S31500411A80E1C6E8C944566AC0FF66C35A42C6CC4756

S31500411A90CFCC77C059FF44C055C0CC47C5D747C501

S31500411AA0D46AC06966C3FFC6C5DEC9445A5F445A93

S31500411AB0E2C04860C9E1E1C6CFCA445AE2C3DBE2AB

S31500411AC0CC48C0CA5A42C35AE2CF556AC0DBC94460

S31500411AD0E7EBC0DEE741DEE7C35CE2CC42C0CAC603

S31500411AE047CFDBE2CC42C0CAC547CFDB4241DBE24E

S31500411AF0C3C5E7CC5C424D5CE2CFE1E1C6DB42C502

S31500411B0041C0CADD42CFDBE2CC41C0CADBE2CF5A9B

S31500411B10E2C0F0EE415AE2C3D76A44DE47C5F6C990

S31500411B204444C94447EDC0D7FF44F57D445A5F4418

S31500411B30C541C0FFFFCF7EFFCF7DFFCF41C0A0DBB8

S31500411B40E2C04160C9E1E1C6D75A44DBE2C35CE287

S31500411B50CC4160CA5CE2CFE1E1C6DB42C55AE2C094

S31500411B60D4CA415AE2C3D8CA4441C0A0E7EBCC65C6

S31500411B7066CFC9E7CFDBE2CF4BE7CFCC47C5C0E75E

S31500411B80CF65E7C344E7C06AEB41E2E1C678CA44A0

S31500411B9055CA4142E1C6FACA44D46AC06566C3C061

S31500411BA06F44CC4B4444E7C069EB4142E1C6C04B6C

S31500411BB0446547C578CA44DB6F44D14B44EBEB419E

S31500411BC042E1C6CC4B446666C042E1C6CFCA4466D2

S31500411BD0C6C5C06F44CC4B44C04B4465E7C042E1E7

S31500411BE0C666CAC541E7C0665A44DBE2CC4260CA12

S31500411BF0DB424D4160CADBE2CF44E7C069EB41C0FD

S31500411C00C0CADB424DDBE2CF4147C56547C5666683

S31500411C10C0E2E1C6C94B444BE7CC4260CA4B474D93

S31500411C204160CA4BE7CFC047C5C94B44C0C0C0C0DD

S31500411C30C0C0F0C0C0EBC0C0EEC0C041C0A0E7EB21

S31500411C40CC7266CFD8FF44656F446CDB446CDB4491

S31500411C506CDB446CDB446C66C0E2E1C6FC4B44443D

S31500411C60E7C0C6ED41E2E1C66CDB44666A445FCC3F

S31500411C7044C0E7C0E2E1C6D7CC4441E74142E1C6B0

S31500411C80CFCA44EDEDC06666C3C9E7CC4160CAC957

S31500411C90E7CFDBE2CC4160CADBE2CF4BE74DE4E183

S31500411CA0C6D1CC44CA47C5DBE2CF66C6C5C6CC441D

S31500411CB0C9E7CCE8C6C550C0CADBE2CF7266CCDB09

S31500411CC0424D65C6C5DDCC44DBE24DDBE24D726675

S31500411CD0CFF04B4444E7C0EEED4142E1C6E8CC4487

S31500411CE0C06F4465CC44D7E7C05CE2C3D7CC44F669

S31500411CF0ED44F04B44F966CCC57D4474CC44D87769

S31500411D00C0E4E1C6414D44D847C5D847C5D877C098

S31500411D1066CC44747D44FACC4477CC446FEDC0D74D

S31500411D20FF44F04B4455FF44C0C0485CE7C042E124

S31500411D30C677CC44DB47C5F04B44747D44FCCC4468

S31500411D4077CC4477CC44DBE4C07BC0C0F0D4C3C07D

S31500411D506F44F04B445CE2C3D46F4142E1C6D14D7E

S31500411D6044F57D446047C556FF44C06F44D7CC44D3

S31500411D70F3ED41E2E1C6D14D44D7CC44C06F44D7DF

S31500411D80CC44F3ED41E2E1C6D14D44FF7E44E74DFB

S31500411D9044F0ED4144E1C6694D44714D4144C0CAE8

S31500411DA05CE2C04460CA5CE2C3D74D44DB6F44EB9E

S31500411DB04D4472EDC078CC4469EB41E24D44E1FFBC

S31500411DC0CF6AC0C07148C34741C050C0C0F044C388

S31500411DD0E2C0C0ED65C0D1D7C041C0A0F64DC5F542

S31500411DE07ECC7466CF6FEECCF666CFD8FF44FF7ECD

S31500411DF044E44E447766C0C0E8C644E7C0E1E1C664

S31500411E006A4E44486048744EC3F6F6C377C6C5CC9D

S31500411E104E4478EE44F6DD44C94E4478EE44CF4E06

S31500411E2044FF4D44F3ED4142E1C6F6DD447766C0D9

S31500411E30566A4142E1C6F6DD44F6EDC0F6EE41E2B0

S31500411E40E1C677DE4471EE4142E1C6E44E44746632

S31500411E50C072EE41E2E1C6D74D44F34E41E2E1C6DE

S31500411E60484D4472EDC0D7FF44F6EDC0D4CA41F6A1

S31500411E70EDC3C94E44F6F64274EE42F6F6C3F6C6D3

S31500411E80C5474E4474C6C0FCFFCFF0CAC06060C5AA

S31500411E90C0D44160C0C06CE2C0FAD1C0D8D2C04102

S31500411EA0C0A0C06F4478DE44FF7E44DB6F44784E69

S31500411EB0C578DE44D8D7C041C0A042E7C0E2E1C6FA

S31500411EC0D2CF44E4E7C0C0E8C6C377C041E1C64BC0

S31500411ED0CF44486048C347C548C0484247C5C0602B

S31500411EE0C6C0CFC5E447C544E7C3C05F44D46FC04D

S31500411EF050CF44CAC0C0C060C06A53C0F3E2C0E418

S31500411F00D7C07D60C0F548C041C0A044E7C069EB79

S31500411F1041E4E1C6E2CF44D46F4144E1C6DBCFC5DB

S31500411F2044E7C0DB5F4441C0A044E7C0F96F41E2EA

S31500411F30E1C674CF44776F41E2E1C6655F44566AB4

S31500411F4041E2E1C6F5CF44786F4142E1C665CFC56E

S31500411F5065CFC565CFC565CFC5655F44DEFFCF5645

S31500411F60C0C06FC0C041C0A0C64247414247FCCF36

S31500411F7044424247FA5F44C559B4C0608841C0A053

S31500411F80F966C05ACC41C9E7C3534B41F966C3C64A

S31500411F906C447466CCC0D8C3F9F6CFD7E7C0C977CD

S31500411FA0C3C048C5C0D84441C0A0F5E2C0CAE7C3D2

S31500411FB063C941F5E2C3C66C44F3E2C04DE7C3C908

S31500411FC0E7C363C941F3E2C3F5E2C05ACC414BE7EB

S31500411FD0C3CAE7C05ACC41CAE7C3C9E741E4E1C62F

S31500411FE0664844CA77C04B77C34BE7C05A48444E0C

S31500411FF078C04160487466CC41E1C6FA48424D77A3

S31500412000CF4D47C54D47C54E48C54ED84441C0A0A2

S315004120105A6CC06966C3F078C07DE844C055C0D7E4

S3150041202047C5DDE7C0EB66C369C6C5FFFF41F0485A

S31500412030C5F0D84441C0A0D4E7C36C6ACC78E4CF9C

S31500412040FAE4CFFCE4CF7EE4C37D78C07D48C54841

S31500412050C0CA6A66C3E2E1C64ECA447D44CF6C66D5

S31500412060C0E2E1C641ED44EDED447DD844D8C944D2

S315004120706A66C0636941E4E1C6D8C944D747CC6CB6

S31500412080EB447844C0D447CC6CEB447B44C06A668D

S31500412090C0636941C6E1C66FC944FCC6CC6CEB441A

S315004120A06FE2C0EDED44C3C0C0E7C944E86ACCEB7A

S315004120B0C9447E66C042E1C6CCEB446A6ACC65EB54

S315004120C04450C048FC66C35F47C5EDED4448C0C0B7

S315004120D0F3C944C9CA446A66C0E7CA41E2E1C6FADD

S315004120E0C9447E66C042E1C6CCEB44666ACC65EB28

S315004120F0446A66C0E7CA4142E1C647CA44FC66C073

S31500412100D44741FC66C37EC6C57E66C0F06941E2DE

S31500412110E1C6CCEB447DD8445A6A44484BCC696607

S31500412120C042E1C67E44CFE46ACC65EB445F47C515

S315004121305A6A446A66C0E7CA4142E1C67DD844FC50

S3150041214066C0D44741FC66C37DD84441C0A05FE721

S31500412150C0636A4142E1C65A5A445FE7C3CCEB4485

S31500412160CCEB445A5A4472C0C07844C0E27ECF7B1D

S3150041217044C07BFFCF6CE2C0F3FFCF6FE2C0F9FFF3

S31500412180CF60C04260C04260C04241C0A041C0A0D1

S315004121904DE44460E8C041C0A0C3EBC36047CC6C8A

S315004121A0EB44C563C053E7C05AE7C34BEBC053E7A3

S315004121B0C3C9EBCC65EB445AE7C053E7C3F35A4472

S315004121C060FC42FFC04241C0A060C04241C0A04144

S315004121D0C0A06FC042CA74C04163C0F0FFCFFA5F6E

S315004121E0C041C0A0D2EBCC65EB4450C0487E66C32B

S315004121F0CCDB444863C07EFFCF41C0A0C0C0484845

S3150041220060CAFC6044E44BC3C074C6537744C0F013

S31500412210C65647C55F4B4465DB4463EB4142E1C665

S31500412220D4DB4465DB44CAC0C0C042C041C0A055EE

S31500412230E7CF55D7CCD4EB44D4EB445547C5E74B10

S315004122404441C0A06C7BC055E7C353EBC0C0E7C354

S315004122507DEB444860485577C37DEB4455D7C3551C

S3150041226077C3C047C57B4B446C4BC56CDB44554774

S31500412270C5714B4441C0A050C0484460CA63EB415C

S3150041228044E1C6EB6A41C5CC417DDB44FAC0C0415D

S31500412290C0A0F966C0F5E241E4E1C6DBED44C65CA7

S315004122A04441C0A0EDED44CC5C44D1CC44CC5C442B

S315004122B0D86CC0FF66C3596CCC65EB44FFC6C553A9

S315004122C0CC44CC5C44C07ECF4DCAC0FFFFCF41C099

S315004122D0A0D8E7CF59E741E2E1C6DB5C44D877CCE9

S315004122E0FA4842EECCC374664DE2E1C65060CA423A

S315004122F0E1C66ACC44DBCCC5DB5C44D8E7C063C9E4

S3150041230041D8E7C3DDCC44C0C044CFED44C6E1C6A5

S31500412310F5CC447E6CC0F36A44FF6CC07DE8444B07

S31500412320D1C0D7E7C0D44741FF6C41D7E7C341EDA0

S3150041233044D747C5C0DD44F0D4C341C0C0F548C009

S3150041234041C0A0D7E7C07D6641E4E1C641DD44D73F

S31500412350E7C07D66C37B6641E4E1C641DD44ED6687

S31500412360C0E2E1C6DBED4441DD4441C0A05A6CC048

S315004123705CE7C3557D44F366C0CFDD446CDBC0CF1B

S31500412380ED44D7E7C37DE844474DC0C0DD4441C075

S31500412390A0E1EDC0F36A44EDC6C5C0FCC6DBDD4431

S315004123A071CCC37166C06C4DC37166C3F0C6C5EBD3

S315004123B0DD447166C06C4DC37166C3EBDD44E4CA4E

S315004123C0C0C050C041C0A0C06CC663C942E2E1C6AC

S315004123D0D2E7C05ACC41ED4D41EDEDC3EDDD44416F

S315004123E0C0A0EE66C0E2E1C6F6DD4450C048C0C0BA

S315004123F0C6EE66CF41EEC0F36A44C0DE4444CAC06D

S3150041240071D4C360F0C060C042C060C06044C06067

S31500412410C042C0C04160CC4160C042C060416078AA

S31500412420C060C042C0C04260604160C042C06042BC

S3150041243060FCC060C042C0C0C3D44D4160C042C010

S3150041244060C36048C060C042C0C04441C9C060F07A

S3150041245044C06044C3EDC06050C5C0C0C5D24D4103

S3150041246060F044C0C048CC4D4160F044C06048D2A1

S315004124704D41604444C0C0C9CC4D41604444C060F4

S31500412480C9C5F9C060C042C060C6C371C0D2C544A7

S31500412490C0E4C6C34D41D2C544C0E8C64471C0D7A5

S315004124A04DC5C06CC6C94D41607444C0F0C6C9C96A

S315004124B041607444C074C6CCE1C06050C5C0FCC61E

S315004124C04EEDC060CC4441E1C65AEDC06044444241

S315004124D0E1C64DEDC060444444E1C65AEDC060CC0E

S315004124E044E1E1C64EEDC0604444E2E1C650EDC070

S315004124F0604444E4E1C650EDC060D44448E2C64D70

S31500412500EDC060D44444E2C641EDC060D44442E2E9

S31500412510C6CFEDC060D44441E2C650EDC0C3554478

S315004125204863C64DEDC0C355444463C641EDC0C37F

S3150041253055444263C6CFEDC0C355444163C6604866

S315004125404160C04260C0C0D4EDC060E444E141474F

S31500412550D44D4160E444E24147D4C94160E444E496

S315004125604147D4C941C66544664147D4EDC060FC84

S3150041257044414247D44DC060FC44424247D4DD41C8

S3150041258060FC44C64247D4EDC06048C5E1C047D46B

S31500412590C9416048C5E2C047D44D416048C5E4C021

S315004125A047D4D1C06048C5E8C047D4EDC060C0C576

S315004125B0414147D44DC060C0C5424147D4DD416029

S315004125C0C0C5444147D4D1C060C0C548414760CC2D

S315004125D0C060C04250C0C0D24D41CCD144C0C0CA37

S315004125E0CC4D41CCD144C060CAD24D4141D144C009

S315004125F0C04BCC4D4141D144C0604BC571C060C058

S3150041260042C0C0CC4471C060C042C060CC44C5C069

S3150041261060C042C0C04D444D4160C042C0604D6043

S3150041262074C060C042C0C04E6050C060C042C0600D

S315004126304ED44D4160D444C0C0CFD44D4160504486

S31500412640C060CFC54D4160C042C0C0C660E4426073

S31500412650C042E765C05A654260C042E265C060E873

S31500412660C360C0426565C0C3D14260C042EDD7C0B8

S31500412670C3D142606044C956C0C5D14260CC4469A9

S3150041268055C053D14260C0426FE4C0D27D42605CC6

S31500412690445665C04141C35355C54DCFC04E5542C1

S315004126A060504463CCC0CFD14260C0C57455C0D1DF

S315004126B0554260D4C559CFC05541C347C9C5C5CF99

S315004126C0C0CC594260CC44C0D8C044F542C65544FA

S315004126D0C050C0C6714860C042C060C0C6C54860EF

S315004126E0C042C0C041C64DC960C042C06041C6F586

S315004126F04860C042C0C042C6D14860C042C0604284

S31500412700D44DC960D844C060C3D14DC9D4C9C5C030

S31500412710C047C94DC9607844C06047CF4D4860CC79

S31500412720C5C0C048D4C5484EC544C0604841D1C95A

S3150041273048F944C0C0C9CCC548477D44C060C9D8E2

S31500412740554860C0C5C0C0CA42C54860CCC5C0C0B6

S31500412750C34EC9C9605044C0C0C0C66548D8654467

S31500412760C0C044D45948606044C060CAD4E148609E

S31500412770D844C0C0C544F54860C042C060C544D1D4

S315004127804860C042C0C0C6D85548D46544C060C63A

S31500412790C9D73C7B42180000000000000000000041

S315004127A000000000D4C5484EC5C3C047C57B4B4455

S315004127B06C4BC56CDB445547C5714B4441C0A05079

S315004127C0C0484460CA63EB4144E1C6EB6A41C5CCAB

S315004127D0417DDB44FAC0C041C0A0F966C0F5E24183

S315004127E0E4E1C6DBED44C65C4441C0A0EDED44CC1A

S315004127F05C44D1CC44CC5C44D86CC0FF66C3596CB4

S31500412800CC65EB44FFC6C553CC44CC5C44C07ECFBB

S315004128104DCAC0FFFFCF41C0A0D8E7CF59E741E23B

S31500412820E1C6DB5C44D877CCFA4842EECCC3746649

S315004128304DE2E1C65060CA42E1C66ACC44DBCCC532

S31500412840DB5C44D8E7C063C941D8E7C3DDCC44C0AB

S31500412850C044CFED44C6E1C6F5CC447E6CC0F36AB4

S3150041286044FF6CC07DE8444BD1C0D7E7C0D4474153

S31500412870FF6C41D7E7C341ED44D747C5C0DD44F0BE

S31500412880D4C341C0C0F548C041C0A0D7E7C07D66AA

S3150041289041E4E1C641DD44D7E7C07D66C37B66417D

S315004128A0E4E1C641DD44ED66C0E2E1C6DBED44410B

S315004128B0DD4441C0A05A6CC05CE7C3557D44F36614

S315004128C0C0CFDD446CDBC0CFED44D7E7C37DE844E0

S315004128D0474DC0C0DD4441C0A0E1EDC0F36A44EDBF

S315004128E0C6C5C0FCC6DBDD4471CCC37166C06C4D48

S315004128F0C37166C3F0C6C5EBDD447166C06C4DC39A

S315004129007166C3EBDD44E4CAC0C050C041C0A0C03B

S315004129106CC663C942E2E1C6D2E7C05ACC41ED4D2D

S3150041292041EDEDC3EDDD4441C0A0EE66C0E2E1C636

S31500412930F6DD4450C048C0C0C6EE66CF41EEC0F396

S315004129406A44C0DE4444CAC071D4C360F0C060C0AA

S3150041295042C060C06044C060C042C0C04160CC411A

S3150041296060C042C060416078C060C042C0C0426041

S31500412970604160C042C0604260FCC060C042C0C0AD

S31500412980C3D44D4160C042C060C36048C060C042CC

S31500412990C0C04441C9C060F044C06044C3EDC0609A

S315004129A050C5C0C0C5D24D4160F044C0C048CC4DB1

S315004129B04160F044C06048D24D41604444C0C0C902

S315004129C0CC4D41604444C060C9C5F9C060C042C0F5

S315004129D060C6C371C0D2C544C0E4C6C34D41D2C569

S315004129E044C0E8C64471C0D74DC5C06CC6C94D4147

S315004129F0607444C0F0C6C9C941607444C074C6CC51

S31500412A00E1C06050C5C0FCC64EEDC060CC4441E15A

S31500412A10C65AEDC060444442E1C64DEDC0604444EF

S31500412A2044E1C65AEDC060CC44E1E1C64EEDC0601A

S31500412A304444E2E1C650EDC0604444E4E1C650ED91

S31500412A40C060D44448E2C64DEDC060D44444E2C6B9

S31500412A5041EDC060D44442E2C6CFEDC060D44441AA

S31500412A60E2C650EDC0C355444863C64DEDC0C3559B

S31500412A70444463C641EDC0C355444263C6CFEDC02D

S31500412A80C355444163C660484160C04260C0C0D43A

S31500412A90EDC060E444E14147D44D4160E444E24144

S31500412AA047D4C94160E444E44147D4C941C6654479

S31500412AB0664147D4EDC060FC44414247D44DC060B5

S31500412AC0FC44424247D4DD4160FC44C64247D4ED12

S31500412AD0C06048C5E1C047D4C9416048C5E2C04766

S31500412AE0D44D416048C5E4C047D4D1C06048C5E82B

S31500412AF0C047D4EDC060C0C5414147D44DC060C058

S31500412B00C5424147D4DD4160C0C5444147D4D1C0E7

S31500412B1060C0C548414760CCC060C04250C0C0D2C9

S31500412B204D41CCD144C0C0CACC4D41CCD144C0604A

S31500412B30CAD24D4141D144C0C04BCC4D4141D14453

S31500412B40C0604BC571C060C042C0C0CC4471C0605A

S31500412B50C042C060CC44C5C060C042C0C04D444DB7

S31500412B604160C042C0604D6074C060C042C0C04E4A

S31500412B706050C060C042C0604ED44D4160D444C034

S31500412B80C0CFD44D41605044C060CFC54D4160C0B7

S31500412B9042C0C0C660E44260C042E765C05A654271

S31500412BA060C042E265C060E8C360C0426565C0C3BB

S31500412BB0D14260C042EDD7C0C3D142606044C956DC

S31500412BC0C0C5D14260CC446955C053D14260C04270

S31500412BD06FE4C0D27D42605C445665C04141C353F7

S31500412BE055C54DCFC04E554260504463CCC0CFD140

S31500412BF04260C0C57455C0D1554260D4C559CFC095

S31500412C005541C347C9C5C5CFC0CC594260CC44C064

S31500412C10D8C044F542C65544C050C0C6714860C08C

S31500412C2042C060C0C6C54860C042C0C041C64DC969

S31500412C3060C042C06041C6F54860C042C0C042C69D

S31500412C40D14860C042C06042D44DC960D844C060DA

S31500412C50C3D14DC9D4C9C5C0C047C94DC96078445F

S31500412C60C06047CF4D4860CCC5C0C048D4C5484E6A

S31500412C70C544C0604841D1C948F944C0C0C9CCC562

S31500412C8048477D44C060C9D8554860C0C5C0C0CA20

S31500412C9042C54860CCC5C0C0C34EC9C9605044C0D6

S31500412CA0C0C0C66548D86544C0C044D45948606070

S31500412CB044C060CAD4E14860D844C0C0C544F54860

S31500412CC060C042C060C544D14860C042C0C0C6D899

S31500412CD05548D46544C060C6C9D73C7B42180000FC

S30E00412CE0000000000000000000A4

S70500000000FA

儈僯僐儞偺俫俬俿俙俠侾侽傪丂俽俹俙俼俿俙俶俁偱幚尰丄偦偺俋丂俵俙俽俽偺婡擻

// SIEVE

ORG X"200"

BGN L BUF

ST BCNT

L M819

ST CNT

L N1

L1 ST ,I BCNT

KCT BCNT

KCT CNT

B L1

// HLT

//

L Z0

ST CNTI

ST CONT

L M819

ST CNT

L BUF

ST BCNT

L4 L ,I BCNT

KNA

B L2

L N3

A CNTI

A CNTI

ST PRIM

A CNTI

ST K

L5 L N819

S K

KPA

B L3

L BUF

A K

ST CLRP

L Z0

ST ,I CLRP

L PRIM

A K

ST K

B L5

L3 KCT CONT

L2 KCT CNTI

KCT BCNT

KCT CNT

B L4

HLT

L BUF

ST BCNT

L M819

ST CNT

L Z0

ST CNTI

L6 L ,I BCNT

KZA

KCT CNTI

KCT BCNT

KCT CNT

B L6

HLT

BUF DC X"400"

BCNT DC 1

M819 DC -2560

N819 DC 2560

CLRP DC 0

CONT DC 0

N3 DC 3

N1 DC 1

Z0 DC 0

CNT DC 0

CNTI DC 0

PRIM DC 0

K DC 0

END BGN

H10>lr410000interval 2400,get 34B

H10>d410000

ADDR 0 1 2 3 4 5 6 7 8 9 A B C D E F ascii

00410000 2F2F 2053 4945 5645 0D0A 2020 4F52 4720 [ // SIEVE.. ORG ]

00410010 2058 2232 3030 220D 0A42 474E 2020 4C20 [ X"200"..BGN L ]

00410020 2042 5546 0D0A 2020 5354 2020 4243 4E54 [ BUF.. ST BCNT]

00410030 0D0A 2020 4C20 204D 3831 390D 0A20 2053 [ .. L M819.. S]

00410040 5420 434E 540D 0A20 204C 2020 4E31 0D0A [ T CNT.. L N1..]

00410050 4C31 2020 5354 2020 2C49 2020 4243 4E54 [ L1 ST ,I BCNT]

00410060 0D0A 2020 4B43 5420 2042 434E 540D 0A20 [ .. KCT BCNT.. ]

00410070 204B 4354 2020 434E 540D 0A20 2042 2020 [ KCT CNT.. B ]

丒丒丒丒丒

H10>mas 410000,418000

PASS 1 END tape =347

PASS 2 END tape =347

PASS 3 END tape =347

H10>

H10>d418000,4180ff

ADDR 0 1 2 3 4 5 6 7 8 9 A B C D E F ascii

00418000 0D0A 0D0A 4243 4E54 2020 3032 3341 0D0A [ ....BCNT 023A..]

00418010 4247 4E20 2020 3032 3030 0D0A 4255 4620 [ BGN 0200..BUF ]

00418020 2020 3032 3339 0D0A 434C 5250 2020 3032 [ 0239..CLRP 02]

00418030 3344 0D0A 434E 5420 2020 3032 3432 0D0A [ 3D..CNT 0242..]

00418040 434E 5449 2020 3032 3433 0D0A 434F 4E54 [ CNTI 0243..CONT]

00418050 2020 3032 3345 0D0A 4B20 2020 2020 3032 [ 023E..K 02]

00418060 3435 0D0A 4C31 2020 2020 3032 3035 0D0A [ 45..L1 0205..]

00418070 4C32 2020 2020 3032 3237 0D0A 4C33 2020 [ L2 0227..L3 ]

00418080 2020 3032 3236 0D0A 4C34 2020 2020 3032 [ 0226..L4 02]

00418090 3130 0D0A 4C35 2020 2020 3032 3139 0D0A [ 10..L5 0219..]

004180A0 4C36 2020 2020 3032 3332 0D0A 4D38 3139 [ L6 0232..M819]

004180B0 2020 3032 3342 0D0A 4E31 2020 2020 3032 [ 023B..N1 02]

004180C0 3430 0D0A 4E33 2020 2020 3032 3346 0D0A [ 40..N3 023F..]

004180D0 4E38 3139 2020 3032 3343 0D0A 5052 494D [ N819 023C..PRIM]

004180E0 2020 3032 3434 0D0A 5A30 2020 2020 3032 [ 0244..Z0 02]

004180F0 3431 0D0A 0000 0000 0000 0000 0000 0000 [ 41..............]

H10>d

ADDR 0 1 2 3 4 5 6 7 8 9 A B C D E F ascii

00418100 0000 0000 0000 0000 0000 0000 0000 0000 [ ................]

00418110 0000 0000 0000 0000 0000 0000 0000 0000 [ ................]

00418120 0000 0000 0000 0000 0000 0000 0000 0000 [ ................]

00418130 0000 0000 0000 0000 0000 0000 0000 0000 [ ................]

00418140 0000 0000 0000 0000 0000 0000 0000 0000 [ ................]

00418150 0000 0000 0000 0000 0000 0000 0000 0000 [ ................]

00418160 0000 0000 0000 0000 0000 0000 0000 0000 [ ................]

00418170 0000 0000 0D0A 3030 3030 490D 0A30 3830 [ ......0000I..080]

00418180 3047 0D0A 3030 3030 490D 0A30 3230 3047 [ 0G..0000I..0200G]

00418190 0D0A 3041 3339 4033 4133 4140 3041 3342 [ ..0A39@3A3A@0A3B]

004181A0 4033 4134 3240 3041 3430 4033 4533 4140 [ @3A42@0A40@3E3A@]

004181B0 3532 3341 4035 3234 3240 0D0A 3432 3035 [ 523A@5242@..4205]

004181C0 4030 4134 3140 3341 3433 4033 4133 4540 [ @0A41@3A43@3A3E@]

004181D0 3041 3342 4033 4134 3240 3041 3339 4033 [ 0A3B@3A42@0A39@3]

004181E0 4133 4140 0D0A 3045 3341 4036 3836 3240 [ A3A@..0E3A@6862@]

004181F0 3432 3237 4030 4133 4640 3132 3433 4031 [ 4227@0A3F@1243@1]

H10>d

ADDR 0 1 2 3 4 5 6 7 8 9 A B C D E F ascii

00418200 3234 3340 3341 3434 4031 3234 3340 0D0A [ 243@3A44@1243@..]

00418210 3341 3435 4030 4133 4340 3141 3435 4036 [ 3A45@0A3C@1A45@6]

00418220 3836 3440 3432 3236 4030 4133 3940 3132 [ 864@4226@0A39@12]

00418230 3435 4033 4133 4440 0D0A 3041 3431 4033 [ 45@3A3D@..0A41@3]

00418240 4533 4440 3041 3434 4031 3234 3540 3341 [ E3D@0A44@1245@3A]

00418250 3435 4034 3231 3940 3532 3345 4035 3234 [ 45@4219@523E@524]

00418260 3340 0D0A 3532 3341 4035 3234 3240 3432 [ 3@..523A@5242@42]

00418270 3130 4036 4630 3040 3041 3339 4033 4133 [ 10@6F00@0A39@3A3]

00418280 4140 3041 3342 4033 4134 3240 0D0A 3041 [ A@0A3B@3A42@..0A]

00418290 3431 4033 4134 3340 3045 3341 4036 3834 [ 41@3A43@0E3A@684]

004182A0 3240 3532 3433 4035 3233 4140 3532 3432 [ 2@5243@523A@5242]

004182B0 4034 3233 3240 0D0A 3646 3030 4030 3430 [ @4232@..6F00@040]

004182C0 3040 3030 3031 4046 3630 3040 3041 3030 [ 0@0001@F600@0A00]

004182D0 4030 3030 3040 3030 3030 4030 3030 3340 [ @0000@0000@0003@]

004182E0 0D0A 3030 3031 4030 3030 3040 3030 3030 [ ..0001@0000@0000]

004182F0 4030 3030 3040 3030 3030 4030 3030 3040 [ @0000@0000@0000@]

H10>d

ADDR 0 1 2 3 4 5 6 7 8 9 A B C D E F ascii

00418300 0D0A 3146 3046 490D 0A30 3042 3947 0D0A [ ..1F0FI..00B9G..]

00418310 3045 4330 4030 4543 3040 0D0A 3144 3830 [ 0EC0@0EC0@..1D80]

00418320 490D 0A30 3039 4647 0D0A 3030 3030 400D [ I..009FG..0000@.]

00418330 0A30 3030 3049 0D0A 3032 3030 480D 0A00 [ .0000I..0200H...]

00418340 0000 0000 0000 0000 0000 0000 0000 0000 [ ................]

00418350 0000 0000 0000 0000 0000 0000 0000 0000 [ ................]

00418360 0000 0000 0000 0000 0000 0000 0000 0000 [ ................]

00418370 0000 0000 0000 0000 0000 0000 0000 0000 [ ................]

00418380 0000 0000 0000 0000 0000 0000 0000 0000 [ ................]

00418390 0000 0000 0000 0000 0000 0000 0000 0000 [ ................]

004183A0 0000 0000 0000 0000 0000 0000 0000 0000 [ ................]

004183B0 0000 0000 0000 0000 0000 0000 0000 000D [ ................]

004183C0 0A20 2020 2020 2030 3030 3049 0D0A 3038 [ . 0000I..08]

004183D0 3030 2020 3038 3030 4720 0D0A 2020 2020 [ 00 0800G .. ]

004183E0 2020 2020 2020 2020 2020 2F2F 2053 4945 [ // SIE]

004183F0 5645 0D0A 2020 2020 2020 3030 3030 490D [ VE.. 0000I.]

H10>d

ADDR 0 1 2 3 4 5 6 7 8 9 A B C D E F ascii

00418400 0A30 3230 3020 2030 3230 3047 2020 2020 [ .0200 0200G ]

00418410 204F 5247 2020 5822 3230 3022 0D0A 3032 [ ORG X"200"..02]

00418420 3030 2020 3041 3339 4020 2020 4247 4E20 [ 00 0A39@ BGN ]

00418430 204C 2020 4255 460D 0A30 3230 3120 2033 [ L BUF..0201 3]

00418440 4133 4140 2020 2020 2053 5420 2042 434E [ A3A@ ST BCN]

00418450 540D 0A30 3230 3220 2030 4133 4240 2020 [ T..0202 0A3B@ ]

00418460 2020 204C 2020 4D38 3139 0D0A 3032 3033 [ L M819..0203]

00418470 2020 3341 3432 4020 2020 2020 5354 2043 [ 3A42@ ST C]

00418480 4E54 0D0A 3032 3034 2020 3041 3430 4020 [ NT..0204 0A40@ ]

00418490 2020 2020 4C20 204E 310D 0A30 3230 3520 [ L N1..0205 ]

004184A0 2033 4533 4140 2020 204C 3120 2053 5420 [ 3E3A@ L1 ST ]

004184B0 202C 4920 2042 434E 540D 0A30 3230 3620 [ ,I BCNT..0206 ]

004184C0 2035 3233 4140 2020 2020 204B 4354 2020 [ 523A@ KCT ]

004184D0 4243 4E54 0D0A 3032 3037 2020 3532 3432 [ BCNT..0207 5242]

004184E0 4020 2020 2020 4B43 5420 2043 4E54 0D0A [ @ KCT CNT..]

004184F0 3032 3038 2020 3432 3035 4020 2020 2020 [ 0208 4205@ ]

H10>d

ADDR 0 1 2 3 4 5 6 7 8 9 A B C D E F ascii

00418500 4220 204C 310D 0A20 2020 2020 2020 2020 [ B L1.. ]

00418510 2020 2020 202F 2F20 2048 4C54 0D0A 2020 [ // HLT.. ]

00418520 2020 2020 2020 2020 2020 2020 2F2F 0D0A [ //..]

00418530 3032 3039 2020 3041 3431 4020 2020 2020 [ 0209 0A41@ ]

00418540 4C20 205A 300D 0A30 3230 4120 2033 4134 [ L Z0..020A 3A4]

00418550 3340 2020 2020 2053 5420 2043 4E54 490D [ 3@ ST CNTI.]

00418560 0A30 3230 4220 2033 4133 4540 2020 2020 [ .020B 3A3E@ ]

00418570 2053 5420 2043 4F4E 540D 0A30 3230 4320 [ ST CONT..020C ]

00418580 2030 4133 4240 2020 2020 204C 2020 4D38 [ 0A3B@ L M8]

00418590 3139 0D0A 3032 3044 2020 3341 3432 4020 [ 19..020D 3A42@ ]

004185A0 2020 2020 5354 2020 434E 540D 0A30 3230 [ ST CNT..020]

004185B0 4520 2030 4133 3940 2020 2020 204C 2020 [ E 0A39@ L ]

004185C0 4255 460D 0A30 3230 4620 2033 4133 4140 [ BUF..020F 3A3A@]

004185D0 2020 2020 2053 5420 2042 434E 540D 0A30 [ ST BCNT..0]

004185E0 3231 3020 2030 4533 4140 2020 204C 3420 [ 210 0E3A@ L4 ]

004185F0 204C 2020 2C49 2020 4243 4E54 0D0A 3032 [ L ,I BCNT..02]

H10>d

ADDR 0 1 2 3 4 5 6 7 8 9 A B C D E F ascii

00418600 3131 2020 3638 3632 4020 2020 2020 4B4E [ 11 6862@ KN]

00418610 410D 0A30 3231 3220 2034 3232 3740 2020 [ A..0212 4227@ ]

00418620 2020 2042 2020 4C32 0D0A 3032 3133 2020 [ B L2..0213 ]

00418630 3041 3346 4020 2020 2020 4C20 204E 330D [ 0A3F@ L N3.]

00418640 0A30 3231 3420 2031 3234 3340 2020 2020 [ .0214 1243@ ]

00418650 2041 2020 434E 5449 0D0A 3032 3135 2020 [ A CNTI..0215 ]

00418660 3132 3433 4020 2020 2020 4120 2043 4E54 [ 1243@ A CNT]

00418670 490D 0A30 3231 3620 2033 4134 3440 2020 [ I..0216 3A44@ ]

00418680 2020 2053 5420 2050 5249 4D0D 0A30 3231 [ ST PRIM..021]

00418690 3720 2031 3234 3340 2020 2020 2041 2020 [ 7 1243@ A ]

004186A0 434E 5449 0D0A 3032 3138 2020 3341 3435 [ CNTI..0218 3A45]

004186B0 4020 2020 2020 5354 2020 4B0D 0A30 3231 [ @ ST K..021]

004186C0 3920 2030 4133 4340 2020 204C 3520 204C [ 9 0A3C@ L5 L]

004186D0 2020 4E38 3139 0D0A 3032 3141 2020 3141 [ N819..021A 1A]

004186E0 3435 4020 2020 2020 5320 204B 0D0A 3032 [ 45@ S K..02]

004186F0 3142 2020 3638 3634 4020 2020 2020 4B50 [ 1B 6864@ KP]

H10>d

ADDR 0 1 2 3 4 5 6 7 8 9 A B C D E F ascii

00418700 410D 0A30 3231 4320 2034 3232 3640 2020 [ A..021C 4226@ ]

00418710 2020 2042 2020 4C33 0D0A 3032 3144 2020 [ B L3..021D ]

00418720 3041 3339 4020 2020 2020 4C20 2042 5546 [ 0A39@ L BUF]

00418730 0D0A 3032 3145 2020 3132 3435 4020 2020 [ ..021E 1245@ ]

00418740 2020 4120 204B 0D0A 3032 3146 2020 3341 [ A K..021F 3A]

00418750 3344 4020 2020 2020 5354 2020 434C 5250 [ 3D@ ST CLRP]

00418760 0D0A 3032 3230 2020 3041 3431 4020 2020 [ ..0220 0A41@ ]

00418770 2020 4C20 205A 300D 0A30 3232 3120 2033 [ L Z0..0221 3]

00418780 4533 4440 2020 2020 2053 5420 202C 4920 [ E3D@ ST ,I ]

00418790 2043 4C52 500D 0A30 3232 3220 2030 4134 [ CLRP..0222 0A4]

004187A0 3440 2020 2020 204C 2020 5052 494D 0D0A [ 4@ L PRIM..]

004187B0 3032 3233 2020 3132 3435 4020 2020 2020 [ 0223 1245@ ]

004187C0 4120 204B 0D0A 3032 3234 2020 3341 3435 [ A K..0224 3A45]

004187D0 4020 2020 2020 5354 2020 4B0D 0A30 3232 [ @ ST K..022]

004187E0 3520 2034 3231 3940 2020 2020 2042 2020 [ 5 4219@ B ]

004187F0 4C35 0D0A 3032 3236 2020 3532 3345 4020 [ L5..0226 523E@ ]

H10>d

ADDR 0 1 2 3 4 5 6 7 8 9 A B C D E F ascii

00418800 2020 4C33 2020 4B43 5420 2043 4F4E 540D [ L3 KCT CONT.]

00418810 0A30 3232 3720 2035 3234 3340 2020 204C [ .0227 5243@ L]

00418820 3220 204B 4354 2020 434E 5449 0D0A 3032 [ 2 KCT CNTI..02]

00418830 3238 2020 3532 3341 4020 2020 2020 4B43 [ 28 523A@ KC]

00418840 5420 2042 434E 540D 0A30 3232 3920 2035 [ T BCNT..0229 5]

00418850 3234 3240 2020 2020 204B 4354 2020 434E [ 242@ KCT CN]

00418860 540D 0A30 3232 4120 2034 3231 3040 2020 [ T..022A 4210@ ]

00418870 2020 2042 2020 4C34 0D0A 0D0A 0D0A 3032 [ B L4......02]

00418880 3242 2020 3646 3030 4020 2020 2020 484C [ 2B 6F00@ HL]

00418890 540D 0A30 3232 4320 2030 4133 3940 2020 [ T..022C 0A39@ ]

004188A0 2020 204C 2020 4255 460D 0A30 3232 4420 [ L BUF..022D ]

004188B0 2033 4133 4140 2020 2020 2053 5420 2042 [ 3A3A@ ST B]

004188C0 434E 540D 0A30 3232 4520 2030 4133 4240 [ CNT..022E 0A3B@]

004188D0 2020 2020 204C 2020 4D38 3139 0D0A 3032 [ L M819..02]

004188E0 3246 2020 3341 3432 4020 2020 2020 5354 [ 2F 3A42@ ST]

004188F0 2020 434E 540D 0A30 3233 3020 2030 4134 [ CNT..0230 0A4]

H10>d

ADDR 0 1 2 3 4 5 6 7 8 9 A B C D E F ascii

00418900 3140 2020 2020 204C 2020 5A30 0D0A 3032 [ 1@ L Z0..02]

00418910 3331 2020 3341 3433 4020 2020 2020 5354 [ 31 3A43@ ST]

00418920 2020 434E 5449 0D0A 3032 3332 2020 3045 [ CNTI..0232 0E]

00418930 3341 4020 2020 4C36 2020 4C20 202C 4920 [ 3A@ L6 L ,I ]

00418940 2042 434E 540D 0A30 3233 3320 2036 3834 [ BCNT..0233 684]

00418950 3240 2020 2020 204B 5A41 0D0A 3032 3334 [ 2@ KZA..0234]

00418960 2020 3532 3433 4020 2020 2020 4B43 5420 [ 5243@ KCT ]

00418970 2043 4E54 490D 0A30 3233 3520 2035 3233 [ CNTI..0235 523]

00418980 4140 2020 2020 204B 4354 2020 4243 4E54 [ A@ KCT BCNT]

00418990 0D0A 3032 3336 2020 3532 3432 4020 2020 [ ..0236 5242@ ]

004189A0 2020 4B43 5420 2043 4E54 0D0A 3032 3337 [ KCT CNT..0237]

004189B0 2020 3432 3332 4020 2020 2020 4220 204C [ 4232@ B L]

004189C0 360D 0A30 3233 3820 2036 4630 3040 2020 [ 6..0238 6F00@ ]

004189D0 2020 2048 4C54 0D0A 3032 3339 2020 3034 [ HLT..0239 04]

004189E0 3030 4020 2020 4255 4620 2044 4320 2058 [ 00@ BUF DC X]

004189F0 2234 3030 220D 0A30 3233 4120 2030 3030 [ "400"..023A 000]

H10>d

ADDR 0 1 2 3 4 5 6 7 8 9 A B C D E F ascii

00418A00 3140 2020 2042 434E 5420 2044 4320 310D [ 1@ BCNT DC 1.]

00418A10 0A30 3233 4220 2046 3630 3040 2020 204D [ .023B F600@ M]

00418A20 3831 3920 2044 4320 2D32 3536 300D 0A30 [ 819 DC -2560..0]

00418A30 3233 4320 2030 4130 3040 2020 204E 3831 [ 23C 0A00@ N81]

00418A40 3920 2044 4320 2032 3536 300D 0A30 3233 [ 9 DC 2560..023]

00418A50 4420 2030 3030 3040 2020 2043 4C52 5020 [ D 0000@ CLRP ]

00418A60 2044 4320 2030 0D0A 3032 3345 2020 3030 [ DC 0..023E 00]

00418A70 3030 4020 2020 434F 4E54 2020 4443 2020 [ 00@ CONT DC ]

00418A80 300D 0A30 3233 4620 2030 3030 3340 2020 [ 0..023F 0003@ ]

00418A90 204E 3320 2044 4320 2033 0D0A 3032 3430 [ N3 DC 3..0240]

00418AA0 2020 3030 3031 4020 2020 4E31 2020 4443 [ 0001@ N1 DC]

00418AB0 2020 310D 0A30 3234 3120 2030 3030 3040 [ 1..0241 0000@]

00418AC0 2020 205A 3020 2044 4320 2030 0D0A 3032 [ Z0 DC 0..02]

00418AD0 3432 2020 3030 3030 4020 2020 434E 5420 [ 42 0000@ CNT ]

00418AE0 2044 4320 300D 0A30 3234 3320 2030 3030 [ DC 0..0243 000]

00418AF0 3040 2020 2043 4E54 4920 2044 4320 300D [ 0@ CNTI DC 0.]

H10>d

ADDR 0 1 2 3 4 5 6 7 8 9 A B C D E F ascii

00418B00 0A30 3234 3420 2030 3030 3040 2020 2050 [ .0244 0000@ P]

00418B10 5249 4D20 2044 4320 2030 0D0A 3032 3435 [ RIM DC 0..0245]

00418B20 2020 3030 3030 4020 2020 4B20 2044 4320 [ 0000@ K DC ]

00418B30 2030 0D0A 2020 2020 2020 3146 3046 490D [ 0.. 1F0FI.]

00418B40 0A30 3042 3920 2030 3042 3947 200D 0A30 [ .00B9 00B9G ..0]

00418B50 3042 3920 2030 4543 3040 200D 0A30 3042 [ 0B9 0EC0@ ..00B]

00418B60 4120 2030 4543 3040 200D 0A20 2020 2020 [ A 0EC0@ .. ]

00418B70 2031 4438 3049 0D0A 3030 3946 2020 3030 [ 1D80I..009F 00]

00418B80 3946 4720 0D0A 3030 3946 2020 3030 3030 [ 9FG ..009F 0000]

00418B90 4020 0D0A 2020 2020 2020 3030 3030 490D [ @ .. 0000I.]

00418BA0 0A20 2020 2020 2030 3230 3048 2020 2020 [ . 0200H ]

00418BB0 2045 4E44 2020 4247 4E0D 0A00 0000 0000 [ END BGN.......]

00418BC0 0000 0000 0000 0000 0000 0000 0000 0000 [ ................]

00418BD0 0000 0000 0000 0000 0000 0000 0000 0000 [ ................]

00418BE0 0000 0000 0000 0000 0000 0000 0000 0000 [ ................]

00418BF0 0000 0000 0000 0000 0000 0000 0000 0000 [ ................]

H10>

0000I

0800G

0000I

0200G

0A39@3A3A@0A3B@3A42@0A40@3E3A@523A@5242@

4205@0A41@3A43@3A3E@0A3B@3A42@0A39@3A3A@

0E3A@6862@4227@0A3F@1243@1243@3A44@1243@

3A45@0A3C@1A45@6864@4226@0A39@1245@3A3D@

0A41@3E3D@0A44@1245@3A45@4219@523E@5243@

523A@5242@4210@6F00@0A39@3A3A@0A3B@3A42@

0A41@3A43@0E3A@6842@5243@523A@5242@4232@

6F00@0400@0001@F600@0A00@0000@0000@0003@

0001@0000@0000@0000@0000@0000@

1F0FI

00B9G

0EC0@0EC0@

1D80I

009FG

0000@

0000I

0200H

0000I

0800 0800G

// SIEVE

0000I

0200 0200G ORG X"200"

0200 0A39@ BGN L BUF

0201 3A3A@ ST BCNT

0202 0A3B@ L M819

0203 3A42@ ST CNT

0204 0A40@ L N1

0205 3E3A@ L1 ST ,I BCNT

0206 523A@ KCT BCNT

0207 5242@ KCT CNT

0208 4205@ B L1

// HLT

//

0209 0A41@ L Z0

020A 3A43@ ST CNTI

020B 3A3E@ ST CONT

020C 0A3B@ L M819

020D 3A42@ ST CNT

020E 0A39@ L BUF

020F 3A3A@ ST BCNT

0210 0E3A@ L4 L ,I BCNT

0211 6862@ KNA

0212 4227@ B L2

0213 0A3F@ L N3

0214 1243@ A CNTI

0215 1243@ A CNTI

0216 3A44@ ST PRIM

0217 1243@ A CNTI

0218 3A45@ ST K

0219 0A3C@ L5 L N819

021A 1A45@ S K

021B 6864@ KPA

021C 4226@ B L3

021D 0A39@ L BUF

021E 1245@ A K

021F 3A3D@ ST CLRP

0220 0A41@ L Z0

0221 3E3D@ ST ,I CLRP

0222 0A44@ L PRIM

0223 1245@ A K

0224 3A45@ ST K

0225 4219@ B L5

0226 523E@ L3 KCT CONT

0227 5243@ L2 KCT CNTI

0228 523A@ KCT BCNT

0229 5242@ KCT CNT

022A 4210@ B L4

022B 6F00@ HLT

022C 0A39@ L BUF

022D 3A3A@ ST BCNT

022E 0A3B@ L M819

022F 3A42@ ST CNT

0230 0A41@ L Z0

0231 3A43@ ST CNTI

0232 0E3A@ L6 L ,I BCNT

0233 6842@ KZA

0234 5243@ KCT CNTI

0235 523A@ KCT BCNT

0236 5242@ KCT CNT

0237 4232@ B L6

0238 6F00@ HLT

0239 0400@ BUF DC X"400"

023A 0001@ BCNT DC 1

023B F600@ M819 DC -2560

023C 0A00@ N819 DC 2560

023D 0000@ CLRP DC 0

023E 0000@ CONT DC 0

023F 0003@ N3 DC 3

0240 0001@ N1 DC 1

0241 0000@ Z0 DC 0

0242 0000@ CNT DC 0

0243 0000@ CNTI DC 0

0244 0000@ PRIM DC 0

0245 0000@ K DC 0

1F0FI

00B9 00B9G

00B9 0EC0@

00BA 0EC0@

1D80I

009F 009FG

009F 0000@

0000I

0200H END BGN

儈僯僐儞偺俫俬俿俙俠侾侽傪丂俽俹俙俼俿俙俶俁偱幚尰丄偦偺侾侽丂慺悢傪媮傔偰傒傞

庤弴侾丂揹尮嵞搳擖偱丄俫俉俁侽俇俋偺儌僯僞偱丄h10m69_22.mot 傪儘乕僪偟偰丄侽倶係侽侽俀俉係偐傜幚峴偡傞丅

庤弴俀丂僾儘儞僾僩偑丄H10> 偵側傞偲丄H10>l40e000 (enter) 偵偟偰偍偄偰丄僷僜僐儞偐傜丄hitac3s14.sr 傪憲怣偟偰丄俫俉偺侽倶係侽俤侽侽侽斣抧偐傜俥俹俧俙偺僐儞僼傿僊儏儗乕僔儑儞僨乕僞傪儘乕僪偡傞丅

庤弴俁丂H10>prog ( enter ) 偱丄俥俹俧俙傪僐儞僼傿僊儏儗乕僔儑儞偡傞丅

偙偺忬懺偱丄俫俬俿俙俠侾侽偑弶婜忬懺偵側偭偰偄傑偡丅

ipl.sr 偙偺僼傽僀儖偼丄俫俉偺傾僪儗僗丄侽倶俀侾侽侽侽侽斣抧偺忣曬偑擖偭偰偄傑偡丅

H10>l220000 ( enter ) 偲僐儅儞僪傪偁偨偊偰丄

僷僜僐儞偺僞乕儈僫儖偐傜丄ipl.sr 傪憲怣偡傞丅

偦偺屻丄俫俉俁侽俇俋偺 侽倶係俁侽侽侽侽斣抧埲崀偵撉傫偩俬俹俴傪

埲壓偺僐儅儞僪偱丄俫俬俿俙俠侾侽偵儘乕僪偡傞丅

H10>load 430000,0,22

俫俬俿俙俠侾侽偺儊儌儕傪妋偐傔傞丅

H10>dmp 0,3f

0000= 0000 0001 7024 8804 3800 7021 4005 7032 [....p$..8.p!@.p2]

0008= 880C 800C 3000 6841 4002 3C01 5001 6842 [....0.hA@.<.P.hB]

0010= 4002 0000 0000 0000 0000 0000 0000 0000 [@...............]

0018= 0000 0000 0000 0000 0000 0000 0000 0000 [................]

0020= 0000 0000 0000 0000 0000 0000 0000 0000 [................]

0028= 0000 0000 0000 0000 0000 0000 0000 0000 [................]

0030= 0000 0000 0000 0000 0000 0000 0000 0000 [................]

0038= 0000 0000 0000 0000 0000 0000 0000 0000 [................]

師偵丄俷俵俴偺僶僀僫儕僼傽僀儖傪丄僷僜僐儞偐傜俫俉俁侽俇俋偵憲傞丅

俷俵俴偼丄tapeoml.bin 偱丄俫俉俁侽俇俋偺侽倶係侾侽侽侽侽偐傜撉傓偵偼丄

H10>lr410000 ( enter )

偲偟偰偍偄偰丄僷僜僐儞偐傜丂tapeoml.bin 傪憲怣偡傞丅

H10>lr410000interval 2400,get 810

俫俉俁侽俇俋偺儊儌儕傪僟儞僾偟偰傒傞偲丄俷俵俴偺僶僀僫儕偑儘乕僪偝傟偰偄傞偼偢丅

H10>d410000

ADDR 0 1 2 3 4 5 6 7 8 9 A B C D E F ascii

00410000 0000 0000 0000 0000 0000 0000 0000 0000 [ ................]

00410010 0110 0400 091E 0404 0111 0400 0712 0008 [ ................]

00410020 0113 060F 0010 0404 0113 0100 041A 0100 [ ................]

00410030 0117 0200 051C 0308 0513 0008 0111 0808 [ ................]

00410040 0014 0300 0513 0308 0111 0400 0212 0800 [ ................]

00410050 0010 0308 0010 0408 0419 0608 0412 0400 [ ................]

00410060 0218 0408 0419 0608 0412 0400 0215 0608 [ ................]

00410070 0616 0400 0212 0108 0617 0608 0416 0400 [ ................]

師偵丄俫俬俿俙俠侾侽偺僥乕僾傪愭摢偵偡傞偨傔丄

H10>tape 0 ( enter ) 偲僐儅儞僪傪梌偊傞丅偙傟偼丄俫俉偺儊儌儕斣抧丄

侽倶係侾侽侽侽侽偐傜偺巻僥乕僾傪丄俫俬俿俙俠侾侽偵撉傑偣傞弨旛偺

僐儅儞僪偱偁傞丅偙偆偟偰偍偄偰丄俫俬俿俙俠侾侽偺俬俹俴傪丄

俀斣抧偐傜俼倀俶丂偝偣傞偲丄俬俹俴偑丄俫俉偺巜掕儊儌儕傪巻僥乕僾偲偟偰

撉傓摦嶌傪偡傞丅tape 0 僐儅儞僪偼丄俫俉偺儊儌儕丄侽倶係侾侽侽侽侽傪

愭摢偲偡傞儊儌儕傪丄巻僥乕僾偺嵟弶偺晹暘偵妱傝摉偰傞僐儅儞僪偱偁傞丅

run 偺偁偲丄俷俵俴傪撉傒廔傢傞偲埲壓偺傛偆側儊僢僙乕僕偑弌偝傟傞丅

H10>run 2

STOP = s , abort = ctrl C

CPU is stop. HLT(6F00) address = 022C. step 1, then run

HLT at PC=005E AC=0000

俫俬俿俙俠侾侽偺儊儌儕傪撉傫偱傒傞偲丄埲壓偺傛偆偵側偭偰偄傞偼偢丅

H10>dmp 0

0000= 0000 4072 7024 8804 3800 7021 4005 7032 [..@rp$..8.p!@.p2]

0008= 880C 800C 3000 6841 4002 3C01 5001 6842 [....0.hA@.<.P.hB]

0010= 4002 0300 4411 4072 0813 6F00 4413 104A [@...D.@r..o.D..J]

0018= 1017 205C 3853 0811 8804 3053 3811 4022 [.. \8S....0S8.@"]

0020= 8000 3800 4849 6842 4028 4849 6842 4025 [..8.HIhB@(HIhB@%]

0028= 6866 4022 1867 6846 4022 1866 6864 4018 [hf@".ghF@".fhd@.]

0030= 185B 6864 4022 6862 4089 1A5B 6866 4017 [.[hd@"hb@..[hf@.]

0038= 8802 1068 383C 0811 405D 3853 8801 6862 [...h8<..@]8S..hb]

0040= 4044 6861 2820 403E 0853 6841 503C 443C [@Dha( @>.ShAP<D<]

0048= 0FFC 0023 0805 3851 0802 3850 0807 3853 [...#..8Q..8P..8S]

0050= 7024 7021 4051 0048 483C 6F00 2060 185C [p$p!@Q.HH<o. `.\]

0058= 4449 3848 4022 0006 002F 8810 6F00 4411 [DI8H@".../..o.D.]

0060= 007F 1800 6842 6F00 4020 4411 FFEF 001C [....hBo.@ D.....]

0068= 4055 8810 1811 3811 8810 3C48 5048 5011 [@U....8...<HPHP.]

0070= 406D 4022 3898 088F 6864 F099 6900 3897 [@m@"8...hd..i.8.]

0078= 68E8 4C90 68E4 4C91 4C92 68E2 4C93 68E1 [h.L.h.L.L.h.L.h.]

偙傟偱俷俵俴偑摦嶌偱偒傞忬懺偵側偭偨偺偱丄僄儔僩僗僥僱僗偺饪偄僾儘僌儔儉丄

sieve_obj.bin 傪僷僜僐儞偐傜俫俉偺儊儌儕偵揮憲偟傑偡丅

僶僀僫儕僼傽僀儖偺揮憲偵偼丄lr 僐儅儞僪傪巊偄傑偡丅乮丂儘乕僪俼俙倂丂偺棯丂乯

俫俉懁偱丄僶僀僫儕僨乕僞庴怣懸偪偆偗忬懺偵偟偰偍偄偰丄僷僜僐儞偐傜

sieve_obj.bin丂傪憲傝傑偡丅俫俉偺傾僪儗僗偼丄侽倶係侾俀侽侽侽偲偟傑偡丅

H10>lr412000interval 2400,get 250

埲忋偱丄揮憲偑廔傢偭偨偺偱丄埲壓偱丄俫俉偺儊儌儕傪妋傔傑偡丅

H10>d412000

ADDR 0 1 2 3 4 5 6 7 8 9 A B C D E F ascii

00412000 0000 0000 0000 0000 0000 0000 0000 0000 [ ................]

00412010 0000 0000 0000 0000 0000 0000 0000 0000 [ ................]

00412020 0000 0000 0000 0000 0000 0000 0000 0000 [ ................]

00412030 0000 0000 0D0A 3030 3030 490D 0A30 3830 [ ......0000I..080]

00412040 3047 0D0A 3030 3030 490D 0A30 3230 3047 [ 0G..0000I..0200G]

00412050 0D0A 3041 3339 4033 4133 4140 3041 3342 [ ..0A39@3A3A@0A3B]

00412060 4033 4134 3240 3041 3430 4033 4533 4140 [ @3A42@0A40@3E3A@]

00412070 3532 3341 4035 3234 3240 0D0A 3432 3035 [ 523A@5242@..4205]

tape 僐儅儞僪偱丄俫俬俿俙俠侾侽偵憲傞僥乕僾僀儊乕僕偺愭摢傪丄侽倶係侾俀侽侽侽

偵偟傑偡丅tape 2000 ( enter ) 偱丄侽倶係侾俀侽侽侽斣抧偲側傝傑偡丅

H10>tape 2000 ( enter )

尰嵼偺僥乕僾撉傒庢傝傾僪儗僗偑偳偙偐偼丄H10>tape ( enter ) 偱妋傔傑偡丅

H10>tape tape=412000 listp=418000

偙偆偟偰偍偄偰丄俷俵俴傪憱傜偣傑偡丅俫俬俿俙俠侾侽偺僗僞乕僩斣抧偼丄

侽倶俀侽丂乮丂儚乕僪傾僪儗僗丂乯側偺偱丄H10>run 20 ( enter ) 偲

僐儅儞僪傪梌偊傞偲丄埲壓偺儊僢僙乕僕偑弌偰丄僄儔僩僗僥僱僗偺饪偄

僾儘僌儔儉偑儘乕僪偝傟傑偡丅

H10>run 20

STOP = s , abort = ctrl C

CPU is stop. HLT(6F00) address = 005F. step 1, then run

HLT at PC=005E AC=0000

俫俬俿俙俠侾侽偺儊儌儕傪妋傔傑偡丅偙偺僾儘僌儔儉偼丄侽倶俀侽侽斣抧

偐傜幚峴偱偒傞傛偆偵丄傾僙儞僽儔偱偐偄偰偄傞偺偱丄埲壓偺傛偆偵丄

俫俬俿俙俠侾侽偺侽倶俀侽侽斣抧傪僟儞僾偟偰尒傑偡丅

H10>dmp 200

0200= 0A39 3A3A 0A3B 3A42 0A40 3E3A 523A 5242 [.9::.;:B.@>:R:RB]

0208= 4205 0A41 3A43 3A3E 0A3B 3A42 0A39 3A3A [B..A:C:>.;:B.9::]

0210= 0E3A 6862 4227 0A3F 1243 1243 3A44 1243 [.:hbB'.?.C.C:D.C]

0218= 3A45 0A3C 1A45 6864 4226 0A39 1245 3A3D [:E.<.EhdB&.9.E:=]

0220= 0A41 3E3D 0A44 1245 3A45 4219 523E 5243 [.A>=.D.E:EB.R>RC]