捛壛 2011.3.4 僾儘僌儔儉儊儌儕偺弶婜壔 丄defparam 嶌惉僣乕儖 乮兝斉 v0.17乯捛壛 2013.8.27

捛壛丂2011.3.24

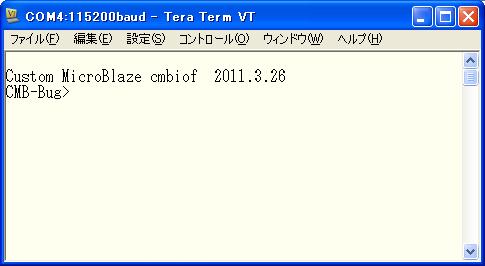

捛壛丂2011.3.26

捛壛丂2011.8.20 丂僾儘僕僃僋僩僼傽僀儖堦幃捛壛丅2011.8.30

捛壛丂2011.8.21 丂僾儘僕僃僋僩僼傽僀儖堦幃捛壛丅2011.8.29

捛壛丂2011.10.24 丂僾儘僕僃僋僩僼傽僀儖堦幃捛壛丅2011.10.24

捛壛丂2011.11.9 丂僾儘僕僃僋僩僼傽僀儖堦幃捛壛丅2011.11.9

僾儘僌儔儉偼僽儘僢僋儊儌儕偺傒偱壜擻丅奜晹儊儌儕偱偼僾儘僌儔儉傪憱傜偣傞偙偲偑偱偒傑偣傫丅俬乛俷丄僨乕僞儊儌儕偺傒巊偊傑偡丅奜晹儊儌儕壜擻亅亅亜怴偨偵嶌惉 傎偲傫偳巊傢傟側偄柦椷偑偁傞丠丠

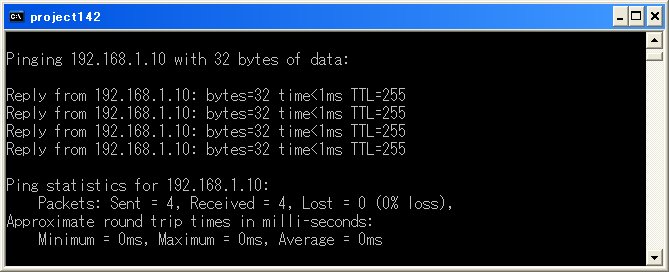

埲壓偼丄怴愝寁偺僇僗僞儉MicroBlaze

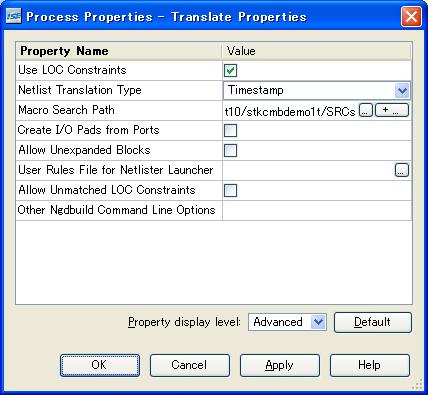

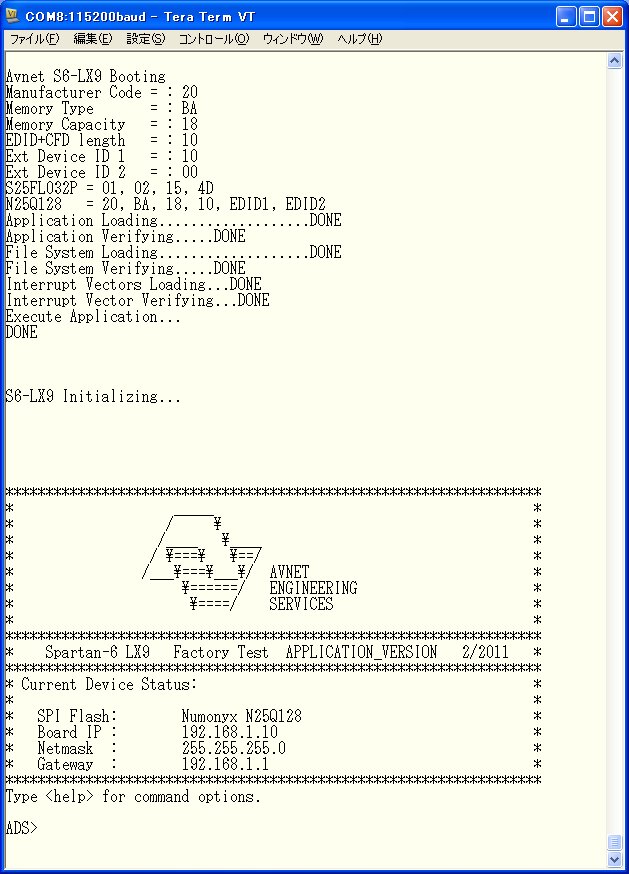

奜晹儊儌儕偱傕摦嶌壜擻側傕偺丅慡偔怴婯偵嶌惉丅僷僀僾儔僀儞側偟丄崅懍僋儘僢僋摦嶌乮俆僋儘僢僋偱侾柦椷乯 幚婡専徹梡丄Hello World! 傪倀俙俼俿偱弌偡乮 Avnet Spartan6 LX9 MicroBoard 乯 僐儞僷僀儔偱嶌惉偟偨僾儘僌儔儉傪憱傜偣傞乮 Avnet Spartan6 LX9 MicroBoard 乯 俴俹俢俢俼儊儌儕偱僾儘僌儔儉傪憱傜偣傞乮 Avnet Spartan6 LX9 MicroBoard 乯 僉儍僢僔儏傪幚憰偟偰僗僺乕僪僥僗僩乮 Avnet Spartan6 LX9 MicroBoard 乯 俽俹俬儊儌儕傪憖嶌偟偰傒傞乮 Avnet Spartan6 LX9 MicroBoard 乯 Xilinx 偺 .ngc 僼傽僀儖傪嶌惉偟偰丄僜乕僗傪僱僢僩儕僗僩偵曄姺 僀乕僒僱僢僩俹俫倄傪憖嶌偟偰傒傞丅俵俙俠偺愝寁乮 Avnet Spartan6 LX9 MicroBoard 乯 僜僼僩偺奐敪偼丄俠尵岅側偳偑巊偊傞偙偲 偦偺僐儞僷僀儔偑柍彏偱巊偊傞偙偲

俤俢俲侾侽偺帒椏偐傜丄俵倝們倰倧俛倢倎倸倕偺柦椷僙僢僩傪挷嵏

俵倝們倰倧俛倢倎倸倕偺柦椷僙僢僩傪傪尒傞偲丄俹倧倵倕倰俹俠偲帡偰偄傞偙偲偑夝傝傑偡偑丄俹倧倵倕倰俹俠偲斾妑偡傞偲偼傞偐偵柦椷悢偑彮側偔丄僶僀僫儕僐乕僪傪尒傞偲丄嬻偒僄儕傾偑懡偄偺偑栚棫偪傑偡丅庡側摿挜傪楍嫇偡傞偲丄

斈梡儗僕僗僞偼俁俀屄偁傞偑丄僴乕僪僂僄傾揑偵丄傑偨偼僜僼僩僂僄傾偱偁傜偐偠傔婡擻偑寛傑偭偰偄傞儗僕僗僞偑偁傞丅

儗僕僗僞丄倰侽丂偼丄撉傒弌偡偲偒丄忢偵侽

儗僕僗僞丄倰侾俆丂偼丄僒僽儖乕僠儞偐傜偺儕僞乕儞傾僪儗僗偵巊傢傟傞丅偙傟偼僴乕僪僂僄傾偱偼側偔僐儞僷僀儔偵傛傞丅

儗僕僗僞丄倰侾係丂偼丄妱傝崬傒敪惗帪偵丄僾儘僌儔儉僇僂儞僞乮俹俠乯偺戅旔偲偟偰丄僴乕僪僂僄傾揑偵巊傢傟傞丅

儗僕僗僞丄倰侾俇丄倰侾俈偼丄僽儗乕僋傗丄椺奜張棟偺偲偒偺俹俠偺抣傪婰壇偡傞丅

儗僕僗僞丄倰侾丂偼丄僜僼僩乮僐儞僷僀儔乯偱巜掕偝傟偨僗僞僢僋億僀儞僞偲側傞丅

柦椷偼丄俁僆儁儔儞僪偺傕偺偑偁傞丅偮傑傝丄儗僕僗僞倰侽丄倰侾丄倰俀側偳偑丄俁屄摨帪偵傾僋僙僗偝傟傞丅

僒僽儖乕僠儞僐乕儖偱偼丄僴乕僪揑偵僗僞僢僋偼巊傢傟偢丄栠傝斣抧奿擺傗僗僞僢僋僼儗乕儉偼僜僼僩偱憖嶌偡傞丅

摨偠偔丄僒僽儖乕僠儞偐傜偺栠傝偼丄栠傝斣抧偑奿擺偝傟偨儗僕僗僞偐傜俹俠偵撉傒弌偝傟傞丅

偄傢備傞丄亙俵俷倁亜柦椷偼側偔丄偨偲偊偽丄倰係傪倰俆偵僐僺乕偡傞偲偒丄倰俆亖倰係亄倰侽偲側傝丄壛嶼柦椷偱幚尰偟偰偄傞丅

俹倧倵倕倰俹俠偱偺俁俀價僢僩懄抣偼丄侾俇價僢僩傪俀夞偵暘偗偰幚尰偟偰偄偨偑丄俵倝們倰倧俛倢倎倸倕偱偼丄俁俀價僢僩柦椷傪俀屄巊偭偰丄晄壜暘偺柦椷偲偟偰幚峴偟丄偪傚偆偳俇係價僢僩柦椷偺傛偆偵怳晳偆丅俹倧倵倕倰俹俠偱偼丄侾夞偺侾俇價僢僩懄抣偼丄俵俽俛偺侾俇價僢僩偵儘乕僪偝傟丄侾夞偩偗偱巊偊傞傛偆偵側偭偰偄傞偑丄俵倝們倰倧俛倢倎倸倕偱偼偦傟偑偱偒側偄丅

偙偪傜偱偡丅inst_mb_ref_guide.pdf 尦偺帒椏偼丄mb_ref_guide.pdf丂偲偄偆俤俢俲侾侽偺俵倝們倰倧俛倢倎倸倕偺僪僉儏儊儞僩偱偡丅墿怓偔僴僀儔僀僩偟偰偄傞柦椷偑丄幚憰偟偨婎杮柦椷偱偡丅俵倝們倰倧俛倢倎倸倕梡偺俠倷倗倵倝値僐儞僷僀儔偑惗惉偡傞僐乕僪傪敳偒弌偟偰偄傑偡丅拞偵偼丄傾僙儞僽儔偱偟偐乮丠乯巊偊側偄柦椷傕幚憰偟偰偄傑偡偑丄偦偺柦椷傪姰慡偵幚峴偱偒傞傢偗偱偼偁傝傑偣傫丅偨偲偊偽丄msr 乮儅僔儞僗僥乕僞僗儗僕僗僞乯偵幚憰偟偨僼儔僌偼丄僉儍儕乕偲丄妱傝崬傒嫋壜僼儔僌偩偗偱偡丅僛儘僼儔僌偲偐丄僒僀儞乮晧乯僼儔僌偲偐偼丄 MicroBlaze 偵偼偁傝傑偣傫偺偱丄僼儔僌椶偼彮側偔偰嵪傒傑偟偨丅柍榑丄俠偺僜乕僗偵丄晜摦彮悢揰側偳偼巊偊傑偣傫偟丄娭楢偡傞 printf() 娭悢傕巊偊傑偣傫丅僨僶僢僌栚揑偱偼 printf() 偑柍偄偲晄曋側偺偱丄惍悢偲暥帤楍偝偊埖偊傟偽傛偄偺偱丄娙扨側傕偺傪嶌偭偰懳墳偟傑偡丅

偲偵偐偔俧俠俠偑揻偒弌偟偨僐乕僪偱摦嶌偡傞傕偺傪栚昗偲偡傞

捛壛丂2011.3.26

傎偲傫偳偺柦椷偱丄侾柦椷侾僋儘僢僋丅僽儔儞僠柦椷丄俁俀價僢僩懄抣柦椷側偳偼俀僋儘僢僋丅

儊儌儕偼丄柦椷丄僨乕僞偑嫟捠丅僔儞僌儖億乕僩愙懕丅僴乕僶乕僪宍幃偼嵟彫峔惉偱儊儌儕傪懡偔巊偆偺偱傗傔傞丅

俽俹俙俼俿俙俶俁偱丄嵟崅俆侽俵俫倸丄倁倝倰倲倕倶係偱俇俇俵俫倸偖傜偄丅柍榑丄幚憰夞楬偑俈侽亾偵憹偊傞偲僗僺乕僪偼丄係侽俵俫倸丄俆侽俵俫倸偑柍擄丅俽俹俙俼俿俙俶俇偱偼丄僎乕僩巊梡棪侾侽亾偱丄俇俇俵俫倸傪妋擣丅乮 SPARTAN6 Evaluation kit SP605 XC6SLX45T 乯

俁僆傌儔儞僪偺儗僕僗僞偼丄RAM16X1D 傪暲傋偰俀宯摑幚憰偟偰丄俁傾僪儗僗懳墳丅

忔嶼丄彍嶼丄僶儗儖僔僼僩側偳偺柦椷丄俵俵倀丄僉儍僢僔儏婡擻側偳側偟丅妱傝崬傒偼壜擻丅

俠俹倀僐傾晹暘偵偼丄倀俙俼俿丄俁俀價僢僩僼儕乕僇僂儞僞侾屄傪撪憻丅

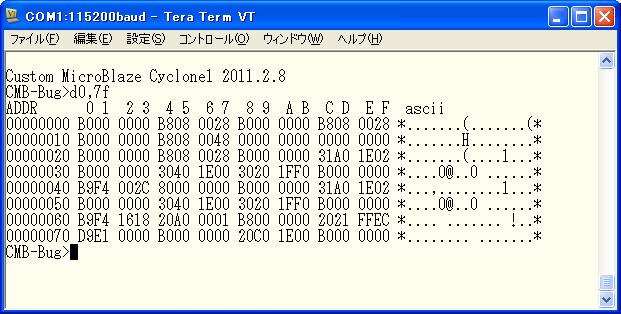

俧俠俠偱僐儞僷僀儖偟偨僐乕僪傪幚峴偱偒傞丅儊儌儕傗丄廃曈儗僕僗僞偺撪梕偺彂偒姺偊丄撉傒弌偟偑峴偊傞娙扨側儌僯僞傪梡堄丅

僗儔僀僗悢偼丄栺侾俁俆侽丅偙傟偼丄俽俹俙俼俿俙俶俁偺丄倃俠俁俽俀侽侽偱俈俆亾傎偳巊偆丅乮SPARTAN3 Starter kit 偱摦嶌乯

儊僀儞儊儌儕偼丄僽儘僢僋俼俙俵 ( RAMB16_S9 ) 傪嵟掅係屄偱摦嶌偡傞偑丄儊儌儕偺弶婜壔僨乕僞嶌惉僣乕儖偱偼丄係屄丄俉屄丄侾俇屄丄俁俀屄傪巊偆傕偺傪梡堄丅

奜晹僶僗偺僗僺乕僪偼丄嵟掅係僋儘僢僋昁梫偩偑丄俽俢俼俙俵傗丄僼儔僢僔儏儊儌儕傪愙懕偟偰僾儘僌儔儉傪摦嶌偝偣傞偙偲偑偱偒傞丅仼掶惓 2012.1.5

奜晹儊儌儕偱偼丄僾儘僌儔儉傪憱傜偣傞偙偲偼偱偒傑偣傫丅俬乛俷丄僨乕僞儊儌儕偺傒巊偊傑偡 俙俴俿俤俼俙偺俠倷們倢倧値倕偱傕摦嶌傪妋擣丅夣挷偵摦偔丅倃俬俴俬俶倃傛傝僋儘僢僋悢傪忋偘傜傟傞偺偱偼側偄偐丠丅俴俤悢偼丄栺係俀侽侽屄 俴俤悢偑懡偄偺偼丄倃倝倢倝値倶偺傛偆偵丄儗僕僗僞傪暘嶶儊儌儕偱嶌傟側偐偭偨堊偲巚傢傟傞丅reg 愰尵偱丄侾侽俀係屄偺僼儕僢僾僼儘僢僾偲丄僨僐乕僟丄儅儖僠僾儗僋僒偱丄俠俹倀僐傾偺係侽亾傪愯傔傞両両

娙扨側傾僙儞僽儔僾儘僌儔儉偱僔儈儏儗乕僔儑儞偟偰傒傞

嵟嬤丄俬俽俤偱偼丄俵倧倓倕倢俽倝倣乮倃倝倢倝値倶丂俤倓倝倲倝倧値乯偑巊偊側偔側傝丄戙傢傝偵丂俬俽俤摨崼偺俬俽倝倣偲側偭偰偄傑偡丅俬俽俤偲偺摑崌偑偱偒偰偄偰丄俙俴俿俤俼俙偺俻倳倎倰倲倳倱俀偲楢摦偡傞丄俵倧倓倕倢俽倝倣偺傛偆側丄偄傠偄傠側愝掕偼晄梫偱偡丅

cmbasm.s 偱偡丅倀俼俴偺娭學忋丄僥僉僗僩僼傽僀儖柤偲偟偰偄傑偡丅

Xilinx MicroBlaze GAS Version 2.9.4 cmbasm.s page 1

1 /*

2 Custom Micro Blaze test asm

3 */

4 .globl _start

5 .section .text

6 .align 2

7 _start:

8 0000 B0001234 addik r3,r0,0x12345678 # 俁俀價僢僩懄抣傪 r3 偵愝掕

8 30605678

9 0008 30800100 addik r4,r0,0x100 # 傾僪儗僗侽倶侾侽侽傪丄 r4 偵愝掕

10 000c F8640000 swi r3,r4,0 # r4 偺傾僪儗僗偵丄r3 傪彂偔

11 0010 E8A40000 lwi r5,r4,0 # r4 偺傾僪儗僗偐傜俁俀價僢僩僨乕僞傪 r5 偵撉傓

12 0014 30A50007 addik r5,r5,7 # r5 偵丂俈 傪壛嶼偡傞丂0x1234567f 偵側傞

13 0018 F8A40000 swi r5,r4,0 # r5 傪丄r4 偺傾僪儗僗偵彂偔

14 001c E8C40004 lwi r6,r4,4 # r4 + 4 偺傾僪儗僗偐傜俁俀價僢僩傪 r6 偵撉傓丅0x0

15 0020 E8C40000 lwi r6,r4,0 # r4 偺傾僪儗僗偐傜俁俀價僢僩傪 r6 偵撉傓丂0x1234567f

16 0024 30C60001 loop: addik r6,r6,1 # r6 偵侾傪壛嶼

17 0028 B810FFFC brid loop # 孞傝曉偟

18 002c 30E70001 addik r7,r7,1 # r7 偵侾傪壛嶼

19 .func

20 .end

21

Xilinx MicroBlaze GAS Version 2.9.4 cmbasm.s page 2

DEFINED SYMBOLS

cmbasm.s:7 .text:00000000 _start

cmbasm.s:16 .text:00000024 loop

NO UNDEFINED SYMBOLS

偙偺儕僗僩偐傜丄摨偠柦椷偱傕丄嵟弶偺 addik 偺傛偆偵僐乕僪偺挿偄傕偺偑偁傝丄俁俀價僢僩懄抣偺偨傔偺丄俬俵俵丂柦椷偑帺摦揑偵捛壛偝傟偰偄傑偡丅傾僙儞僽儔儗儀儖偱偼婰弎偑摨偠偱傕丄弌棃忋偑偭偨僶僀僫儕僐乕僪偱偼丄俬俵俵丂柦椷偑捛壛偝傟偨偙偲偵側偭偰偄傑偡丅偙偙偱丄傛偔娤嶡偡傞偲丄俬俵俵丂柦椷偼丄僽儔儞僠柦椷丄brid丂偲丄傛偔帡偰偄偰丄俵俽俛係價僢僩偑摨偠丄侽倶俛丂偲側偭偰偄傑偡丅撪晹偺摦嶌偱傕俀柦椷傪晄壜暘偵幚峴偡傞僔乕働儞僗偲側傝傑偡丅僽儔儞僠柦椷丂brid 偱偼丄loop 偵栠傞偗傟偳傕丄偦偺師偺柦椷丄addik r7,r7,1 傕幚峴偟偰偟傑偄傑偡丅偙偆偄偆偺傪丄抶墑暘婒偲屇傇傜偟偄偱偡偑丄儖僱僒僗偺俽俫僔儕乕僘儅僀僐儞偱傕摨偠偱偡偹丅撪晹偺僷僀僾儔僀儞偵庢傝崬傑傟偨柦椷傪幪偰偢偵幚峴偟偰丄岠棪傪偁偘傞庤朄偱偡丅

僾儘僌儔儉儊儌儕偺弶婜壔丄defparam 偺俀俆俇價僢僩弶婜壔僨乕僞偺夦

偙偺曽朄偼丄傑偨暿偺婡夛偵傗偭偰傒傛偆偲巚偄傑偡丅

module mainmem( addr,wdata,rdata,clk,we

);

input [15:2] addr;

input [31:0] wdata;

output [31:0] rdata;

input clk;

input [3:0] we;

wire [3:0] dop;

RAMB16_S36 ram0(.DO(rdata[31:0]), .DOP(dop[3:0]), .ADDR(addr[10:2]), .CLK(clk),

.DI(wdata[31:0]), .DIP(4'h0),. EN(1'b1), .SSR(1'b0), .WE(we[3:0] != 0));

丂defparam ram0.INIT_00 = 256'h0000000000000000000000000000000000000000000000009ABCDEF012345678;

endmodule

偲偄偆婰弎偵側傝傑偡丅侽斣抧偑侽倶侾俀俁係俆俇俈俉偱偡偑丄僨乕僞偺俴俽俛偑偦偺傑傑丄defparam 偺俀俆俇價僢僩僨乕僞偺塃抂偵側偭偰偄偰丄偄傢備傞丄僀儞僥儖僾儘僙僢僒偺儊儌儕傊偺僶僀僩僆乕僟乕偱偁傞丄little丂endian 偺暲傃偱偁傞偙偲偑敾傝傑偡丅RAMB16_S1_S36 傪巊偭偨偲偟偰丄侾價僢僩懁偐傜弴偵撉傒弌偡偲丄侽丆侽丆侽丆侾偲側傝傑偡丅偲傕偁傟丄偙傟偼丂倃倝倢倝値倶偺摿惈丂偱偼側偔丄verilog 偺婰弎婯懃側偺偱偦偺傑傑巊偆偟偐偁傝傑偣傫丅

忋婰偵帵偟偨僥僗僩僾儘僌儔儉 傪丄RAMB16_S36 偵愝掕偡傞偵偼丄

丂defparam ram0.INIT_00 = 256'hE8C40004F8A4000030A50007E8A40000F86400003080010030605678B0001234;

丂defparam ram0.INIT_01 = 256'h0000000000000000000000000000000030E70001B810FFFC30C60001E8C40000;

module mainmem( addr,wdata,rdata,clk,we

);

input [15:2] addr;

input [31:0] wdata;

output [31:0] rdata;

input clk;

input [3:0] we;

wire [3:0] dop;

RAMB16_S9 ram0(.DO(rdata[31:24]), .DOP(dop[3]), .ADDR(addr[12:2]), .CLK(clk), .DI(wdata[31:24]),

.DIP(1'b0),. EN(1'b1), .SSR(1'b0), .WE(we[3]));

RAMB16_S9 ram1(.DO(rdata[23:16]), .DOP(dop[2]), .ADDR(addr[12:2]), .CLK(clk), .DI(wdata[23:16]),

.DIP(1'b0),. EN(1'b1), .SSR(1'b0), .WE(we[2]));

RAMB16_S9 ram2(.DO(rdata[15:8]), .DOP(dop[1]), .ADDR(addr[12:2]), .CLK(clk), .DI(wdata[15:8]),

.DIP(1'b0),. EN(1'b1), .SSR(1'b0), .WE(we[1]));

RAMB16_S9 ram3(.DO(rdata[7:0]), .DOP(dop[0]), .ADDR(addr[12:2]), .CLK(clk), .DI(wdata[7:0]),

.DIP(1'b0),. EN(1'b1), .SSR(1'b0), .WE(we[0]));

丂defparam ram0.INIT_00=256'h000000000000000000000000000000000000000030B830E8E8F830E8F83030B0;

丂defparam ram1.INIT_00=256'h0000000000000000000000000000000000000000E710C6C4C4A4A5A464806000;

丂defparam ram2.INIT_00=256'h000000000000000000000000000000000000000000FF00000000000000015612;

丂defparam ram3.INIT_00=256'h000000000000000000000000000000000000000001FC01000400070000007834;

endmodule

Microsoft 倁俠亄亄俀侽侽俆梡儔儞僞僀儉 嵞斝晍壜擻僷僢働乕僕 偑昁梫側応崌偑偁傝傑偡丅

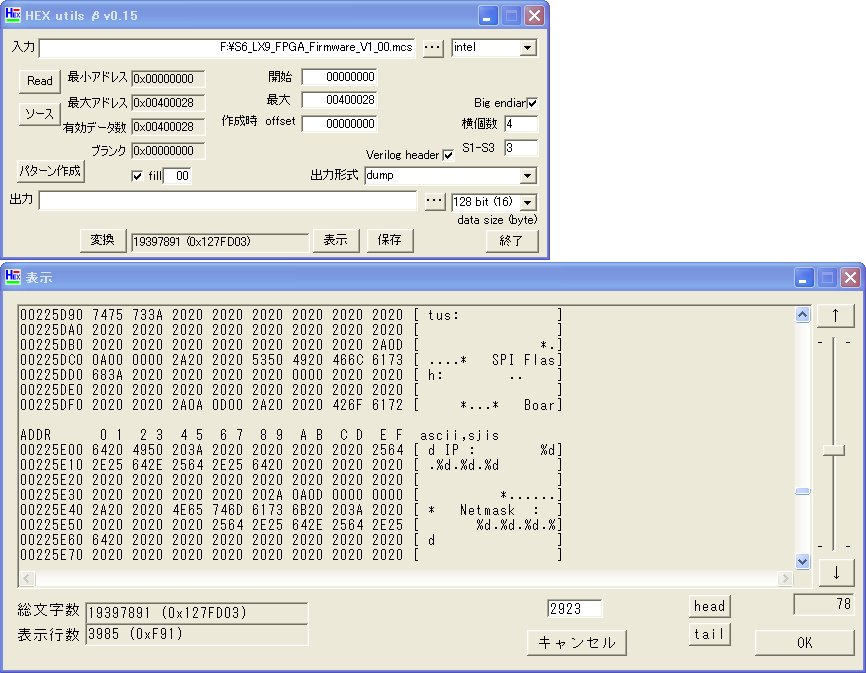

僜乕僗懳墳偼丄儌僩儘乕儔俽丄僀儞僥儖俫俤倃丄俠俽倁丄扨弮俫俤倃偺梾楍丄僶僀僫儕(bin)丄偡傋偰乮僶僀僫儕埖偄乯

弌椡宍幃偼丄defparam丄mif丄俠俽倁丄儌僩儘乕儔俽丄僀儞僥儖俫俤倃丄俻倳倎倰倲倳倱嘦俫俤倃丄僶僀僫儕丄儊儌儕僟儞僾丅

defparam 偺応崌偼丄Xilinx 偺丂BRAM 傪丄僶僗暆侾丆俀丆係丆俉丆侾俇丆俁俀價僢僩傪巜掕偱偒傑偡丅偨偩偟弌棃忋偑傞儊儌儕僷僢僋偼俁俀價僢僩偺儊儌儕偺傒丅

撪晹僶僢僼傽乕偼侾俇俵俛丅偙傟埲忋偺僶僀僫儕偱偺挿偝偵偼枹懳墳丅撉傒崬傒帪偵偼丄傾僪儗僗忣曬傪侽倶侽侽俥俥俥俥俥俥偱儅僗僋丅

僀儞僥儖俫俤倃丄儌僩儘乕儔俽偺応崌偼丄弌椡帪偵丄傾僪儗僗堏摦偑壜擻丅

defparam mif csv Quartus2hex bin 側偳偱偼丄弌椡帪偵尦偺愭摢傾僪儗僗偼丄侽斣抧偲傒側偟傑偡丅

撉傒崬傒帪偵丄僶僢僼傽乕傪丄巜掕僨乕僞乮僶僀僩偺傒乯偱枮偨偡婡擻偑偁傝傑偡丅傑偨偦傟傪偟側偄慖戰傕偁傞偺偱丄俀屄偺僼傽僀儖傪儅乕僕偡傞偙偲偑偱偒傑偡丅僆乕僶乕儔僢僾偟偰傕寈崘偼偱傑偣傫丅

儌僩儘乕儔俽丄僀儞僥儖俫俤倃丄俠俽倁丄mif 側偳偱丄僶僀僩僆乕僟乕傪巜掕偱偒傑偡丅偮傑傝丄僄儞僨傿傾儞曄姺婡擻丅偩偩偟丄侾俇丄俁俀價僢僩扨埵偺傒丅

媽兝斉偼偙偪傜丅v0.1 丂 媽兝斉0.11偼偙偪傜丅v0.11 丂 媽兝斉偼偙偪傜丅v0.12

媽兝斉偼偙偪傜丅v0.13

媽兝斉偼偙偪傜丅v0.14

媽兝斉偼偙偪傜丅v0.15

媽兝斉偼偙偪傜丅v0.16

怴兝斉偼偙偪傜丅v0.17 偙偺僣乕儖偼丄VC++2005 偱嶌惉偟偰偄傞偺偱丄 Microsoft 倁俠亄亄俀侽侽俆梡儔儞僞僀儉 嵞斝晍壜擻僷僢働乕僕 偑昁梫側応崌偑偁傝傑偡丅

庡側巊偄曽

庡側巇條丅嵟戝僜乕僗僒僀僘丗俁俀俵俛丄嵟戝撪晹僨乕僞僶僢僼傽乕丗侾俇俵俛丄嵟戝弌椡僒僀僘丗俀俆俇俵俛丅

傾僪儗僗晅偒俫俤倃僨乕僞偼丄撪晹偵撉傓偲偒丄傾僪儗僗抣傪丄侽倶侽侽俥俥俥俥俥俥偱俙俶俢偟偰偄傑偡丅

塃忋偺慖戰僐儞儃儃僢僋僗偱丄僜乕僗偺僼傽僀儖僞僀僾傪巜掕偟傑偡丅

偦偺偡偖嵍偑丄僽儔僂僓丅僽儔僂僓偱傕僼傽僀儖僞僀僾傪慖戰偱偒傑偡偑丄僐儞儃儃僢僋僗偑桪愭偟傑偡丅

僼傽僀儖偑懚嵼偡傟偽丄僼傽僀儖柤偺愨懳僷僗偑昞帵偝傟傑偡丅

嵍忋偺丄Read 儃僞儞偱丄僼傽僀儖傪撉傒傑偡丅僼傽僀儖僞僀僾偱巜掕偟偨曽朄偱丄撪晹偺僶僢僼傽乕偵撉傒丄嵟彫傾僪儗僗丄側偳偵曬崘偟傑偡丅

僽儔儞僋偼丄搑拞偱傾僪儗僗偑憹壛偟偰丄僨乕僞巜掕偺柍偐偭偨晹暘偺僶僀僩悢傪帵偟傑偡丅fill 偱巜掕偝傟偨抣偺傑傑偱偡丅

fill 僠僃僢僋儃僞儞偑桳岠偩偲丄僼傽僀儖傪撉傓慜偵僶僢僼傽乕傪塃偺抣偱枮偨偟傑偡丅抣偼俀寘偺僿僉僒偱巜掕偟傑偡丅

fill 僠僃僢僋儃僞儞偑柍岠偩偲丄僶僢僼傽乕傪偦偺傑傑偱丄暿偺僼傽僀儖傪撉傒懌偡偙偲偑偱偒傑偡丅

Display 儃僞儞偱丄僜乕僗僼傽僀儖傪暿僂僀儞僪僂偵昞帵偟傑偡丅僜乕僗偑僶僀僫儕巜掕偺応崌偼丄昞帵偟傑偣傫丅

奐巒丂偼丄僶僢僼傽乕偵撉傑傟偨愭摢傾僪儗僗偱丄偙偙偼曄峏偡傞偙偲偑偱偒傑偡丅

廔椆亄侾丂偼丄僶僢僼傽乕偵撉傑傟偨嵟廔傾僪儗僗亄侾偱丄偙偙偼曄峏壜擻偱偡丅

嶌惉帪丂offset 偼丄弌椡偑丄僀儞僥儖俫俤倃丄儌僩儘乕儔俽偺偲偒偺傒桳岠偱丄傾僪儗僗忣曬傪曄峏偱偒傑偡丅

Big endian 偼丄Quartus嘦.mif, Quartus嘦 hex, Excel 僼傽僀儖側偳偵弌椡偡傞偲偒偵桳岠偱丄僶僀僩僆乕僟乕傪曄姺偟傑偡丅

墶屄悢偼丄Excel .CSV僼傽僀儖, 0xHEX, HEX, 側偳偱桳岠偱丄侾峴偺僨乕僞屄悢傪巜掕偟傑偡丅

S1-S3 偼丄儌僩儘乕儔俽儗僐乕僪偱弌椡偡偺偲偒偺傒桳岠偱丄傾僪儗僗暆傪巜掕偟傑偡偑丄傾僪儗僗忣曬偑戝偒偄応崌偼丄俽俀丄俽俁偵側傝傑偡丅

data size (byte) 偼丄defparam 偺応崌偼丄僽儘僢僋俼俙俵侾屄偺僶僗暆傪巜掕偟丄俁俀價僢僩暆儊儌儕偺弶婜壔僨乕僞偵偟傑偡丅

data size (byte) 偼丄mif, Quartus嘦 hex, .CSV, 0xHEX, HEX, 偺応崌偱丄侾屄偺僨乕僞偺僶僗暆傪巜掕偟傑偡丅俉丆侾俇丆俁俀偺傒桳岠偱偡丅

弌椡宍幃偺 僐儞儃儃僢僋僗偼丄弌椡偺僼傽僀儖僞僀僾傪巜掕偟丄偦偺壓偺僽儔僂僓偱僼傽僀儖柤傪巜掕偟傑偡丅

曄姺偼丄撪晹偵撉傑傟偨僶僢僼傽乕偐傜丄弌椡僼傽僀儖傪嶌惉偟傑偡丅昞帵偱丄妋擣偱偒丄曐懚偱僼傽僀儖偵彂偒傑偡丅

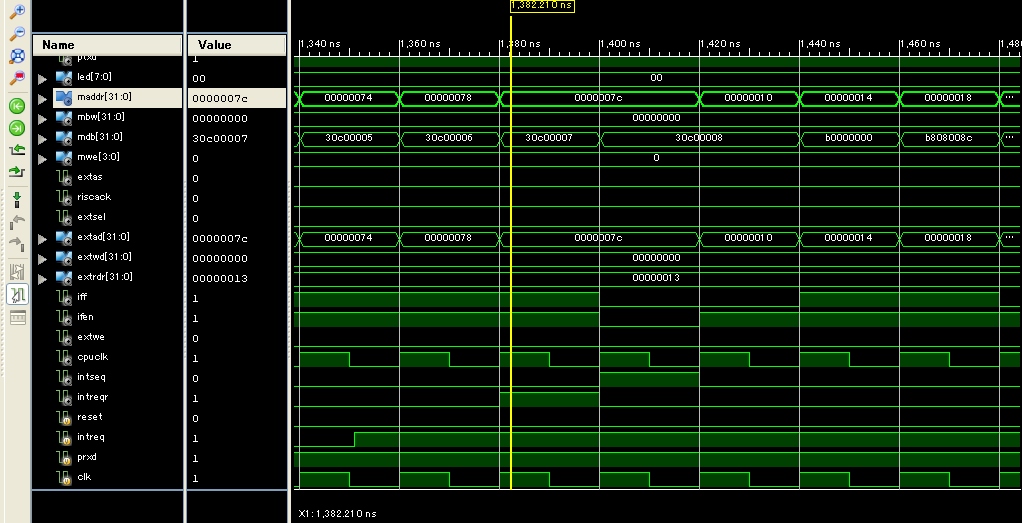

怣崋柤丄intreq 偑丄僞僀儅乕偱敪惗偝偣偨丄奜晹偐傜偺妱傝崬傒梫媮怣崋丅俫倝倗倛傊偺曄壔偱桳岠丅

墿怓偺廲僇乕僜儖偺埵抲偱丄怣崋柤 intreqr 偑侾偵側偭偰偄傑偡偑丄偙傟偑俠俹倀撪晹偱妱傝崬傒梫媮偺棫偪忋偑傝僄僢僕傪専弌偟偨僼儔僌偱偡丅偙偺怣崋偼丄Custom MicroBlaze 偺丂risc2s.ngc 偺弌椡億乕僩偱嶲徠偱偒傞丄testout[4] ( intreqr ) 偱偡丅

intreqr 偺侾僋儘僢僋屻偺怣崋丄intseq 偑丄俠俹倀偑丄妱傝崬傒僔乕働儞僗偵堏峴偟偨偙偲傪帵偟傑偡丅偙偺僞僀儈儞僌偱丄iff丄ifen 偑俴倧倵乮柍岠乯偵側偭偰偄偰丄儊儌儕偵偼丄師偺幚峴傾僪儗僗偑弌偝傟偰偄偰丄柦椷傕撉傒弌偝傟偰偄偰傕乮丂柦椷偼丄侽倶俁侽俠侽侽侽侽俉丂addik r6,r0,8 乯丄幪偰偰偟傑偆偙偲傪帵偟偰偄傑偡丅

師偺僋儘僢僋偱丄俠俹倀偺僾儘僌儔儉僇僂儞僞偑侽倶侾侽偲側偭偰丄maddr 偵侽倶侾侽偑弌偝傟丄ifen 偑桳岠偲側傝丄柦椷僼僃僢僠僗僥乕僩偵堏偭偰偄傑偡丅

師偺僋儘僢僋偱丄儊儌儕偺侽倶侾侽斣抧偺柦椷丄侽倶俛侽侽侽侽侽侽侽偑撉傒弌偝傟偰丄iff 桳岠偱丄柦椷傪幚峴偟偰偄傞偙偲傪帵偟偰偄傑偡丅

幚婡丄Digilent Spartan-3 Starter kit 偱偺妱傝崬傒僥僗僩

俢倝倗倝倢倕値倲偼丄倃倝倢倝値倶偺嫵堢梡昡壙婎斅偺儊乕僇乕偱丄悢擭慜偵埲壓偺婎斅傪弌偟偰偄傑偟偨丅摉帪丄侾俆丆侽侽侽墌傎偳偱丄偐側傝埨偐偭偨偲巚偄傑偡丅偙偺婎斅傪帩偭偰偄傞恖偼偐側傝偄傞偺偱偼側偄偐偲巚偄傑偡丅巊偭偰偄傞俬俠偼丄XC3S200FT256 偱丄棤偵侾俇價僢僩暆偺俽俼俙俵傪俀屄幚憰偝傟偰偄偰丄僆儕僕僫儖偺僨儌夞楬偱偼丄倁俧俙偵暥帤傪弌偟丄憖嶌偼丄 Pico Blaze 偱偟偨丅MicroBlaze 傪擖傟傞偵偼丄儘僕僢僋悢偑懌傜側偐偭偨偺偩偲巚偄傑偡丅

俠俹倀偼丄risc2s.ngc 偱偡(丩佂丮;;) 夝愢偼傑偩偁傝傑偣傫丅

俽俫俀梡儌僯僞 偲傎偲傫偳摨偠偱偡丅

Xilinx Spartan-6 FPGA SP605 Evaluation kit 偱偺摦嶌僥僗僩丄摨偠 risc2s.ngc, mainmem.v 傪巊偭偰偄傑偡

偙偺儃乕僪偱偡偑丄侾俀倁偐傜奺揹尮傪嶌偭偰偄傑偡偑丄傎偲傫偳偑揹尮儌僕儏乕儖偵側偭偰偍傝丄曄姺岠棪偑埆偄傜偟偔丄偐側傝敪擬偟偰怗傟側偔側傝傑偡丅摨婜惍棳僞僀僾偺僗僥僢僾僟僂儞俢俠俢俠僐儞僶乕僞乕側傜丄傕偭偲岠棪偑偄偄偼偢偱丄俋俆亾傎偳偵側傞偼偢偱偡丅偙偺婎斅偺揹尮愝寁偼偐側傝庤敳偒偱偡偹丅 丂sp605cmbiof1.lzh丂 丂仼傾僋僙僗偱偒側偄応崌偼擔傪偁傜偨傔偰偔偩偝偄丅

弨旛拞

Xilinx Virtex4 ML403 Evaluation Platform偱偺摦嶌僥僗僩丄摨偠 risc2s.ngc, mainmem.v 傪巊偭偰偄傑偡

丂ml403cmbiof.lzh丂 丂仼傾僋僙僗偱偒側偄応崌偼擔傪偁傜偨傔偰偔偩偝偄丅

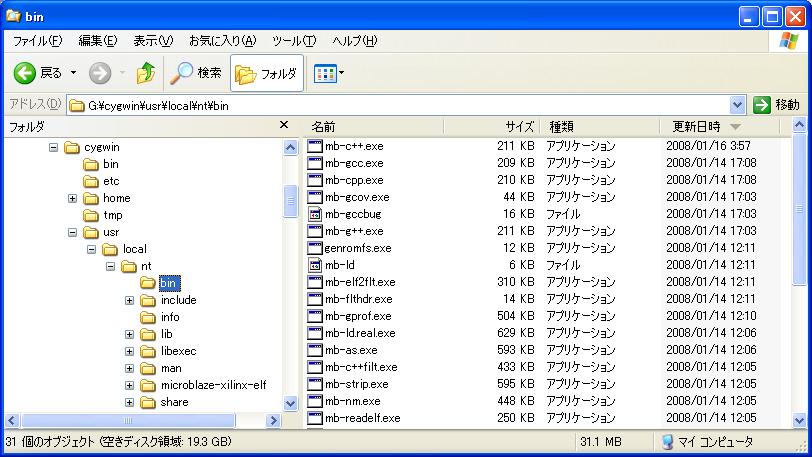

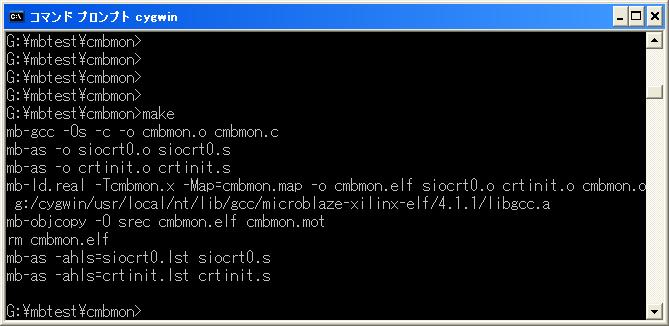

弨旛拞 嵟嬤偺俬俽俤偱偼乮俬俽俤丂v侾俁丏侾偱妋擣乯丄倂倕倐俹倎們倠傪僀儞僗僩乕儖偡傞偲丄俤俢俲僼僅儖僟傕嶌惉偝傟丄偦偺拞偵丂gnu 僼僅儖僟傕偁傝丄microblaze\nt 僼僅儖僟埲壓偵偦傟傜偟偄僐儞僷僀儔僣乕儖偑偁傝傑偡偑丄偙偺丂nt 僼僅儖僟埲壓傪丂Cygwin 偺丄usr\local 僼僅儖僟埲壓偵僐僺乕偟偰丄僷僗傪捠偟偰傕丄巊偊側偄傛偆偱偡丅 偦偺戙傢傝丄俽俢俲偺傒傪僀儞僗僩乕儖偟偰丄gnu 僼僅儖僟埲壓偵揥奐偝傟傞丄microblaze\nt 僼僅儖僟傪僐僺乕偡傞偲丄巊偊傞傛偆偱偡丅傑偨偙偺僣乕儖偼丄Cygwin 娐嫬偑柍偔偰傕巊偊傞傕偺偱偡丅偨偩丄make.exe 側偳傪巊偆偵偼丄gnuwin\bin丂僼僅儖僟偵僷僗傪捠偡昁梫偑偁傞傛偆偱偡丅

俵倝們倰倧俛倢倎倸倕 偺僐儞僷僀儔傪俢俷俽僾儘儞僾僩偱憖嶌偟偰傒傞

makefile丂僐儞僷僀儔傗傾僙儞僽儔丄偦偺懠偺儐乕僥傿儕僥傿乕傪惂屼偡傞丄儊僀僋僼傽僀儖丅

cmbmon.c丂俵倝們倰倧俛倢倎倸倕梡偺儌僯僞丅儊儌儕僟儞僾傗儊儌儕曄峏側偳傪峴偆僾儘僌儔儉丅

siocrt0.s丂僼儗乕儉億僀儞僞傗丄僗僞僢僋億僀儞僞傪愝掕偡傞丄揹尮俷俶屻偵幚峴偝傟傞僾儘僌儔儉

crtinit.s丂曄悢弶婜愝掕傗丄僋儕傾傪峴偆僒僽儖乕僠儞丅

cmbmon.x丂儕儞僇乕僗僋儕僾僩丅奺僙僋僔儑儞傪巜掕偡傞丅

偙偙偱丄cmbmon.c 埲奜偼丄堦搙嶌惉偡傞偲丄偁傑傝曄峏偡傞昁梫偑側偔丄傑偨丄偐側傝斈梡揑側傕偺側偺偱丄埲壓偵偦偺椺傪弌偟偰偍偒傑偡丅

/*

MicroBlaze Vector Map for standalone executables

Address Vector type Label

------- ----------- ------

# 0x00 # (-- IMM --)

# 0x04 # Reset _start1

# 0x08 # (-- IMM --)

# 0x0c # Software Exception _exception_handler

# 0x10 # (-- IMM --)

# 0x14 # Hardware Interrupt _interrupt_handler

# 0x18 # (-- IMM --)

# 0x1C # Breakpoint Exception (-- Don't Care --)

# 0x20 # (-- IMM --)

# 0x24 # Hardware Exception _hw_exception_handler

*/

.globl _start

.section .vectors.reset, "ax"

.align 2

_start:

brai _start1

.section .vectors.sw_exception, "ax"

.align 2

_vector_sw_exception:

# brai _exception_handler

brai _start1

.section .vectors.interrupt, "ax"

.align 2

_vector_interrupt:

# brai _interrupt_handler

brai _start2

.section .vectors.hw_exception, "ax"

.align 2

_vector_hw_exception:

# brai _hw_exception_handler

brai _start1

.section .text

.globl _start1

.align 2

_start1:

la r13, r0, _SDA_BASE_ /* Set the Small Data Anchors and the stack pointer */

la r2, r0, _SDA2_BASE_

la r1, r0, 0x3FF0 /* 16 bytes (4 words are needed by crtinit for args and link reg */

# la r1, r0, _stack-16 /* 16 bytes (4 words are needed by crtinit for args and link reg */

brlid r15, _crtinit /* Initialize BSS and run program */

nop

# addi r1, r1, 16

/* Fall through to exit */

# bri sio

_start2:

la r13, r0, _SDA_BASE_ /* Set the Small Data Anchors and the stack pointer */

la r2, r0, _SDA2_BASE_

la r1, r0, 0x3FF0 /* 16 bytes (4 words are needed by crtinit for args and link reg */

# la r1, r0, _stack-16

brlid r15, main /* Execute the program */

addi r5, r0, 1

/*

exit

Our simple exit

*/

.globl exit

.section .text

.align 2

.ent exit

exit:

bri exit

.end exit

/* 偙偺僜乕僗偼丄俤俢俲俉丏俀偺僒儞僾儖偼丄crtinit.s 傪尦偵曄峏偟偰嶌惉偟偰偄傑偡 */

.globl _crtinit

.align 2

.ent _crtinit

_crtinit:

addi r1, r1, -20 /* Save Link register */

sw r15, r1, r0

addi r6, r0, __sbss_start /* clear SBSS */

addi r7, r0, __sbss_end

rsub r18, r6, r7

blei r18, .Lendsbss

.Lloopsbss:

sw r0, r6, r0

addi r6, r6, 4

rsub r18, r6, r7

bgti r18, .Lloopsbss

.Lendsbss:

addi r6, r0, __bss_start /* clear BSS */

addi r7, r0, __bss_end

rsub r18, r6, r7

blei r18, .Lendbss

.Lloopbss:

sw r0, r6, r0

addi r6, r6, 4

rsub r18, r6, r7

bgti r18, .Lloopbss

.Lendbss:

# brlid r15, _program_init /* Initialize the program */

# nop

# brlid r15, __init /* Invoke language initialization functions */

# nop

addi r6, r0, 0 /* Initialize argc = 1 and argv = NULL and envp = NULL */

addi r7, r0, 0

brlid r15, main /* Execute the program */

addi r5, r0, 0

# brlid r15, __fini /* Invoke language cleanup functions */

# nop

# brlid r15, _program_clean /* Cleanup the program */

# nop

lw r15, r1, r0 /* Return back to CRT */

rtsd r15, 8

addi r1, r1, 20

.end _crtinit

/* Script for ld -r: link without relocation */

OUTPUT_FORMAT("elf32-microblaze", "",

"")

/*SEARCH_DIR("/edkgnu/jm/mb/release/nt/mb/microblaze-xilinx-elf/lib");*/

ENTRY(_start)

_TEXT_START_ADDR = DEFINED(_TEXT_START_ADDR) ? _TEXT_START_ADDR : 0x50;

_HEAP_SIZE = DEFINED(_HEAP_SIZE) ? _HEAP_SIZE : 0x0;

_STACK_SIZE = DEFINED(_STACK_SIZE) ? _STACK_SIZE : 0x400;

SECTIONS

{

.vectors.reset 0x0 : { KEEP (*(.vectors.reset)) } = 0

.vectors.sw_exception 0x8 : { KEEP (*(.vectors.sw_exception)) } = 0

.vectors.interrupt 0x10 : { KEEP (*(.vectors.interrupt)) } = 0

.vectors.debug_sw_break 0x18 : { KEEP (*(.vectors.debug_sw_break)) } = 0

.vectors.hw_exception 0x20 : { KEEP (*(.vectors.hw_exception)) } = 0

.text : {

}

.init : { KEEP (*(.init)) } =0

.fini : { KEEP (*(.fini)) } =0

.rodata : {

; /* Is this needed? */

}

/* Alignments by 8 to ensure that _SDA2_BASE_ on a word boundary */

/* Note that .sdata2 and .sbss2 must be contiguous */

. = ALIGN(8);

_ssrw = .;

.sdata2 : {

}

.sbss2 : {

}

_essrw = .;

_ssrw_size = _essrw - _ssrw;

PROVIDE (_SDA2_BASE_ = _ssrw + (_ssrw_size / 2 ));

.data : {

; /* Is this needed? */

}

/* Added to handle pic code */

.got : {

}

.got1 : {

}

.got2 : {

}

/* Added by Sathya to handle C++ exceptions */

.eh_frame : {

}

.jcr : {

}

.gcc_except_table : {

}

/* Alignments by 8 to ensure that _SDA_BASE_ on a word boundary */

/* Note that .sdata and .sbss must be contiguous */

. = ALIGN(8);

_ssro = .;

.sdata : {

}

.sbss : {

PROVIDE (__sbss_start = .);

*(.sbss)

*(.gnu.linkonce.sb.*)

PROVIDE (__sbss_end = .);

}

_essro = .;

_ssro_size = _essro - _ssro;

PROVIDE (_SDA_BASE_ = _ssro + (_ssro_size / 2 ));

. = ALIGN(4);

_fbss = .;

.bss : {

PROVIDE (__bss_start = .);

*(.bss)

*(.gnu.linkonce.b.*)

*(COMMON)

. = ALIGN(4);

PROVIDE (__bss_end = .);

. += 0x100;

_stack = .;

}

.tdata : {

}

.tbss : {

}

}

MicroBlaze 偺柦椷僙僢僩偱丄傎偲傫偳巊傢傟側偄柦椷偑偁傞丂丠丠

# 偙偙偱丄r4 偑敾掕懳徾偲偟偰丄梡堄偝傟偰偄傞偲偡傞丅

addik r3,r0,bunki_hanntei

rsubik r3,r3,bunki_saki

bunki_hanntei:

beq r4,r3 # r4 偑侽側傜丄PC = PC + r3 偲側傞丅

...

...

bunki_saki:

...

...

俛俤俻俬柦椷傪巊偆偲丄師偺柦椷偱丄忋婰偲摨偠摦嶌傪偟傑偡丅

# 偙偙偱丄r4 偑敾掕懳徾偲偟偰丄梡堄偝傟偰偄傞偲偡傞丅

beqi r4,bunki_saki

...

...

bunki_saki:

...

...

奜晹儊儌儕偱傕摦嶌偱偒傞丄怴偨側僇僗僞儉愝寁偺 MicroBlaze丂俆僋儘僢僋乛侾柦椷

摦嶌僥僗僩拞偵敾柧偟傑偟偨偑丄俤俢俲侾係丏俀乮丂EDK 僼僅儖僟偺丄gnu 僼僅儖僟埲壓偵僀儞僗僩乕儖偝傟偰偄傞乯偺僐儞僷僀儔偱偼丄摦嶌偟側偄偙偲偑敾柧偟傑偟偨丅偙偙偱巊偭偰偒偰偄傞俤俢俲偺俧俠俠僐儞僷僀儔偼丄俤俢俲侾侽丏侾偺傕偺偱丄俧俠俠係丏侾丏侾偲側偭偰偄傑偡丅崱屻偼俤俢俲侾係丏俀偺俧俠俠僣乕儖僠僃乕儞乮俧俠俠係丏俇丏俀乯偵曄偊傛偆偲巚偭偨偗傟偳丄侾係丏俀偺MicroBlaze Core 偵偄偔偮偐柦椷偑捛壛偝傟偰偄偰丄偦傟偑尨場偐斲偐丄尰嵼挷嵏拞偱偡丅 仺仺丂俤俢俲侾係丏俀偺僐儞僷僀儔偱偼摦偐側偐偭偨尨場偼丄僨傿儗僀僗儘僢僩偱偺柦椷偵丄儘乕僪丄僗僩傾柦椷傪巊偭偰偄偰丄偦傟偑怴傜偟偄 Custom MicroBlaze 偱偼惓偟偔幚峴偱偒側偐偭偨堊偩偲敾傝傑偟偨丅俧俠俠係丏侾丏侾偺丂MicroBlaze 僋儘僗僐儞僷僀儔偱偼丄僨傿儗僀僗儘僢僩晅偒偺 brlid 柦椷偺師偵偼丄swi 傗丄lwi 側偳偺儊儌儕傾僋僙僗柦椷傪攝抲偟偰偍傜偢丄儔僀僽儔儕( libgcc.a libm.a ) 偱傕巊傢傟偰偄傑偣傫丅

柦椷僼僃僢僠偼丄傾僪儗僗僗僩儘乕僽侾僋儘僢僋偲丄儊儌儕偐傜偺傾僋僲儕僢僕偺嵟抁俀僋儘僢僋丅

柦椷僨僐乕僪偼侾僋儘僢僋丅撪晹柦椷僐乕僪偵曄姺丅

柦椷幚峴偼丄侾僋儘僢僋偐丄俀僋儘僢僋偺慖戰偱丄捠忢俀僋儘僢僋丅

寢壥奿擺偼丄儗僕僗僞偺応崌侾僋儘僢僋偲偡傞偑丄師偺傾僪儗僗僗僩儘乕僽偺帪揰偱幚峴丅偙偺偨傔侽僋儘僢僋丅

寢壥奿擺偑儊儌儕偺応崌丄傾僪儗僗僗僩儘乕僽侾僋儘僢僋丄傾僋僲儕僢僕偺嵟抁俀僋儘僢僋丅

儊儌儕偐傜偺傾僋僲儕僢僕傪懸偮偺偱丄抶偄儊儌儕偱傕摦嶌壜擻丅撪晹僽儘僢僋儊儌儕偱偼傾僋僲儕僢僕偱侾僋儘僢僋丅

妱傝崬傒偼丄僨傿儗僀僗儘僢僩偑桳傞応崌偼庴偗晅偗側偄丅傑偨丄IMM 柦椷偺応崌傕庴偗晅偗側偄丅偙傟傜偼幚幙揑偵俇係價僢僩柦椷偲側傝丄暘妱偱偒側偄丅--> 嵟嬤偺俤俢俲偱偼丄暘妱偟偨埵抲偱妱傝崬傒傪庴偗晅偗傞傛偆偱偡丅

妱傝崬傒偲娭學偡傞俵俽俼偺僼儔僌"俬俤"偼丄俵俿俽偲俵俥俽偱憖嶌偱偒傞丅懠偼僉儍儕乕僼儔僌偲丄俤俤僼儔僌偺傒憖嶌壜擻丅

忋婰偲娭楢偟偰丄枹掕媊柦椷傪幚峴偟傛偆偲偟偨応崌丄俵俽俼偺俤俤僼儔僌偑侾偩偲丄侽倶俀侽斣抧偵僕儍儞僾偡傞丅偙偺偲偒俤俤僼儔僌偑僋儕傾偝傟傞丅rted 柦椷偼幚憰偟側偄丅俤俤僼儔僌傪憖嶌偡傞偵偼丄mts 柦椷傪巊偆丅枹掕媊柦椷偼丄俵俽俛俇價僢僩偺僐乕僪偱幚憰偟偰偄側偄柦椷偺傎偐丄偱偒傞偩偗懡媊偵搉偭偰敾掕偡傞丅偙傟偼丄丂break 柦椷傪幚憰偟側偄戙傢傝偵丄枹掕媊柦椷偱俤倶們倕倫倲倝倧値傪敪惗偝偣丄僜僼僩僂僄傾傗丄僴乕僪僂僄傾傪娷傔偨僨僶僢僌偵棙梡偟傛偆偲偄偆堄恾偱偁傞丅

俁俀屄偺儗僕僗僞僼傽僀儖偼丄倃倝倢倝値倶愱梡偵偡傞偲丄僽儘僢僋俼俙俵偱偼側偔丄暘嶶儊儌儕偵側傞丅RAM16X1D 僾儕儈僥傿僽傪巊梡丅

忋婰偱reg 愰尵傪峴偆偲丄倃倝倢倝値倶偱偼僽儘僢僋俼俙俵偵側傝丄俙俴俿俤俼俙偱傕摦嶌壜擻傪栚巜偡丅乮傑偩枹妋擣乯

僉儍僢僔儏傪搵嵹壜擻傪峫椂丅僟僀儗僋僩儅僢僺儞僌偱丄柦椷僉儍僢僔儏偺傒側傜斾妑揑彫婯柾偱壜擻偲巚傢傟傞丅

俵俵倀婡擻傪搵嵹壜擻傪峫椂丅---> 偙傟偼丄Linux 傪憱傜偣傞偖傜偄偺栚揑偟偐側偄偲巚傢傟傞丅搵嵹偡傞偲偟偰傕丄俤俢俲偵崌傢偣側偄偲巊偄暔偵側傜側偄丅偦傟偵丄偐側傝夞楬婯柾偑戝偒偔側傞傜偟偄丅

僽乕僩婡擻傪搵嵹壜擻傪峫椂丅僽乕僩婡擻偼丄侽x俥俥俥俥俥俉侽侽偁偨傝偐傜幚峴偟丄奜晹僼儔僢僔儊儌儕丄俽俹俬儊儌儕側偳偐傜丄俢俼俙俵傗撪晹僽儘僢僋俼俙俵偵僐僺乕偟偰婲摦偱偒傞婡擻丅

俧俠俠偺儅僀僋儘僽儗乕僘僐儞僷僀儔偑惗惉偡傞僐乕僪傪幚峴壜擻丅彍嶼丄僶儗儖僔僼僩丄晄摦彫悢揰側偳偼僜僼僩偺儔僀僽儔儕傪巊偄丄僴乕僪僂僄傾柦椷偼摉柺僀儞僾儕儊儞僩偟側偄丅

埲壓偼丄奣棯僽儘僢僋恾丅俠俹倀偺柤徧偼丄risc4s 偲偟偰偄傑偡丅摉弶丄係僋儘僢僋偱侾柦椷偺梊掕偩偭偨偺偱丄偙偺柤慜偵側偭偰偄傑偡偑丄俆僋儘僢僋偱侾柦椷偵側傝傑偟偨丅

俙倁俶俤俿 偺惢昳偱丄廐寧揹巕捠彜偱擖庤偱偒傞傕偺偱偡丅偙偺儃乕僪偱偼丄偨傇傫夞楬婯柾傪戝偒偔偟偰傕丄侾侽侽俵俫倸偱摦嶌偡傞偲巚傢傟傑偡丅婎杮峔惉偱丄栺係俇亾偺僗儔僀僗巊梡棪偲側傝丄婎杮偩偗側傜丄侾俀侽俵俫倸偺摦嶌傪妋擣偟偰偄傑偡丅

俙倁俶俤俿偺僒僀僩 偐傜丄懡偔偺僒儞僾儖僨僓僀儞僼傽僀儖傪僟僂儞儘乕僪偱偒傑偡丅

儗僕僗僞僼傽僀儖傪梡堄偟傑偡丅俁俀價僢僩偺儗僕僗僞傪俁俀屄偱丄俁億乕僩偵偟傑偡丅俁億乕僩儊儌儕偼昗弨偱柍偄偺偱丄俀億乕僩傪俀屄巊偄丄儔僀僩帪偵偼摨偠僨乕僞傪彂偄偰丄忢偵摨堦偺撪梕偵側傞傛偆偵偟偰偍偒傑偡丅僔儈儏儗乕僔儑儞偱偼丄reg 愰尵偱傕偄偄偱偡偑丄幚婡偵僀儞僾儕儊儞僩偡傞偲偒偼丄寢峔側梕検偵側偭偰偟傑偄傑偡丅僼儕僢僾僼儘僢僾偑侾侽俀係屄偵側傞偺偱丄偙傟偩偗偱俆侾俀僗儔僀僗偵傕側偭偰偟傑偄傑偡偐傜丄倃倝倢倝値倶偺暘嶶儊儌儕偱嶌惉偟傑偡丅RAM16X1D( 16 bit 儊儌儕 ) 傪俇係屄巊偭偰丄俁俀屄偺儗僕僗僞偲偟丄偦傟傪俀慻偱俁億乕僩儊儌儕偲偟傑偡丅

儊儌儕偵僀儞僗僩儔僋僔儑儞僼僃僢僠柦椷傪弌偡丅儊儌儕偼僥僗僩儀儞僠懁偱梡堄偟偰偍偔丅

僥僗僩儀儞僠懁偱梫媮偵墳偊傞丅傾僪儗僗偼側偔丄僨乕僞僶僗偵弴斣偵柦椷傪弌偡偩偗偲偟傑偡丅

僨乕僞偑妋掕乮俙俠俲墳摎傪尒傞乯偡傞偲丄僨僐乕僟偱婡擻傪怳傝暘偗傞丅俙俢俢俬丄俙俢俢丄俼俽倀俛丄俙俶俢丄俷俼丄倃俷俼丄側偳傪帋偟偰傒傑偡丅

嶌惉偟偨丄娙扨側僔儈儏儗乕僔儑儞偺 僜乕僗堦幃 偱偡丅(old version )

俬俽俤侾係丏俀傪僀儞僗僩乕儖偟偨僼僅儖僟傪丄f:\xilinx\ 偲偡傞偲丄

set path=f:\xilinx\14.2\ISE_DS\EDK\gnuwin\bin;f:\xilinx\14.2\ISE_DS\EDK\gnu\microblaze\nt\bin;%PATH%

傪丄path1.bat 側偳偺僼傽僀儖柤偱僥僉僗僩僼傽僀儖偱曐懚偟丄僐儅儞僪儔僀儞偐傜丄path1 ( enter ) 偲幚峴丅

偦偺屻丄僐儅儞僪儔僀儞偱丄current_dir>mb-gcc --version ( enter ) 偱

current_dir>mb-gcc --version

mb-gcc (GCC) 4.6.2 20111018 (Xilinx 14.2 Build EDK_P.27 12 Jun 2012)

Copyright (C) 2011 Free Software Foundation, Inc.

This is free software; see the source for copying conditions. There is NO

warranty; not even for MERCHANTABILITY or FITNESS FOR A PARTICULAR PURPOSE.

偲昞帵偝傟傟偽 gnu TOOL 偑巊偊傑偡丅

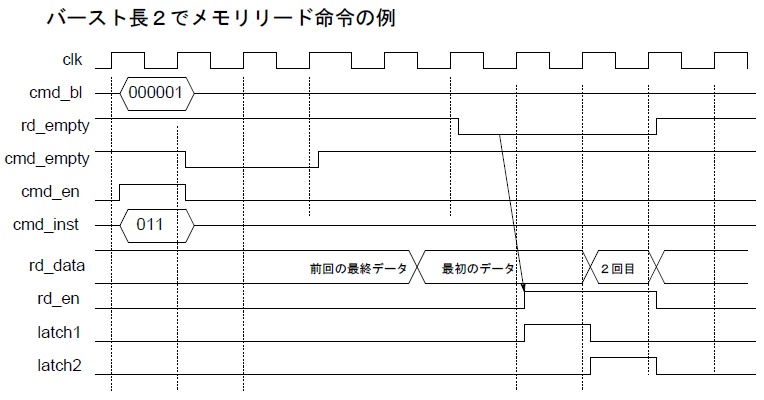

hexutils.exe 兝0.17 柦椷僼僃僢僠(2)丂亜丂柦椷僨僐乕僪(1)丂亜丂柦椷幚峴(2)丂亜丂儊儌儕儕乕僪(2)丂亜丂儗僕僗僞偵儔僀僩(1)

嶌惉偟偨丄儘乕僪丄僗僩傾柦椷傪捛壛偟偨 僜乕僗堦幃 偱偡丅

Xilinx MicroBlaze GAS Listing asmtest.s page 1

1 # Custom MicroBlaze 僥僗僩僾儘僌儔儉

2 .globl _start

3 .section .vectors.reset, "ax"

4 .align 2

5 _start:

6 # r6 <= 0x98765432 偺MSB 16bit 偑丄IMM 柦椷偵側傝丄師偵 addi r6,r0,0x5432 偵側傞

7 0000 B0009876 addi r6,r0,0x98765432

7 20C05432

8 0008 00E63000 add r7,r6,r6 # r7 <= 0x30ECA864 寢壥僉儍儕乕僼儔僌偑侾偵側傞

9 000c 28E70000 addic r7,r7,0 # r7 <= 0x30ECA865 寢壥僉儍儕乕僼儔僌偑壛嶼偝傟傞

10 0010 21000100 addi r8,r0,0x100 # 傾僪儗僗 0x100

11 0014 F8C80000 swi r6,r8,0 # 0x100 斣抧偵丄0x98765432丂傪僗僩傾

12 0018 F8E80004 swi r7,r8,4 # 0x104 斣抧偵丄0x30ECA865丂傪僗僩傾

13 001c E8880000 lwi r4,r8,0 # 0x100 斣抧偐傜丂0x98765432丂傪 r4 偵撉傓

14 0020 E8E80004 lwi r7,r8,4 # 0x104 斣抧偐傜丂0x30ECA865丂傪 r7 偵撉傓

15 0024 20400011 addi r2,r0,0x11 # r2 偵 0x11 傪儘乕僪

16 0028 F0480002 sbi r2,r8,2 # 0x102 斣抧偵丄僶僀僩偱 0x11 傪僗僩傾

17 002c E8880000 lwi r4,r8,0 # 0x100 斣抧偐傜丂0x98761132丂傪 r4 偵撉傓

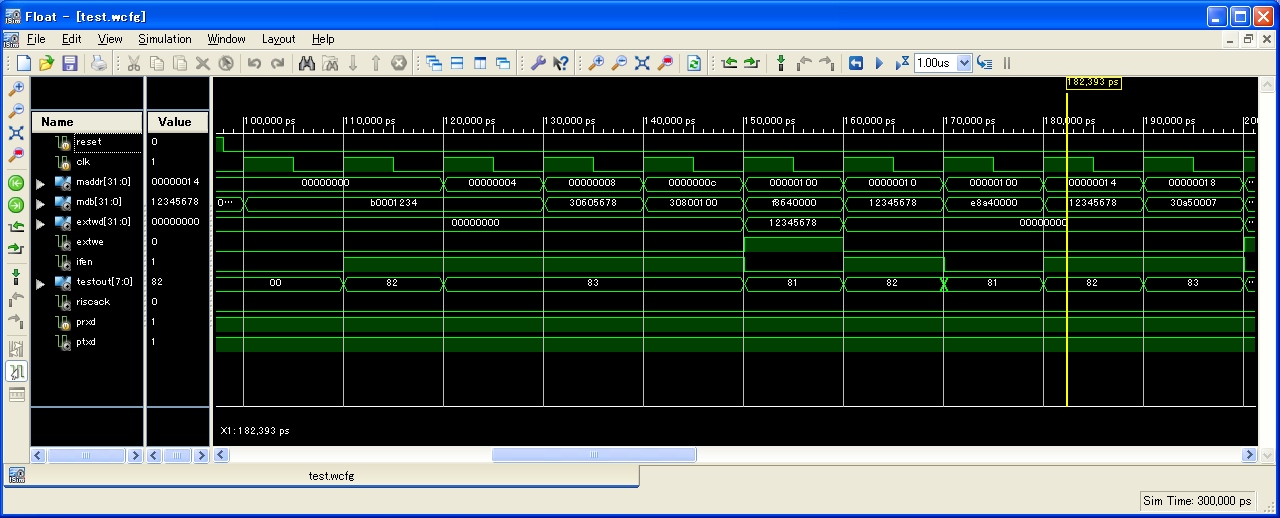

18 0030 80000000 nop

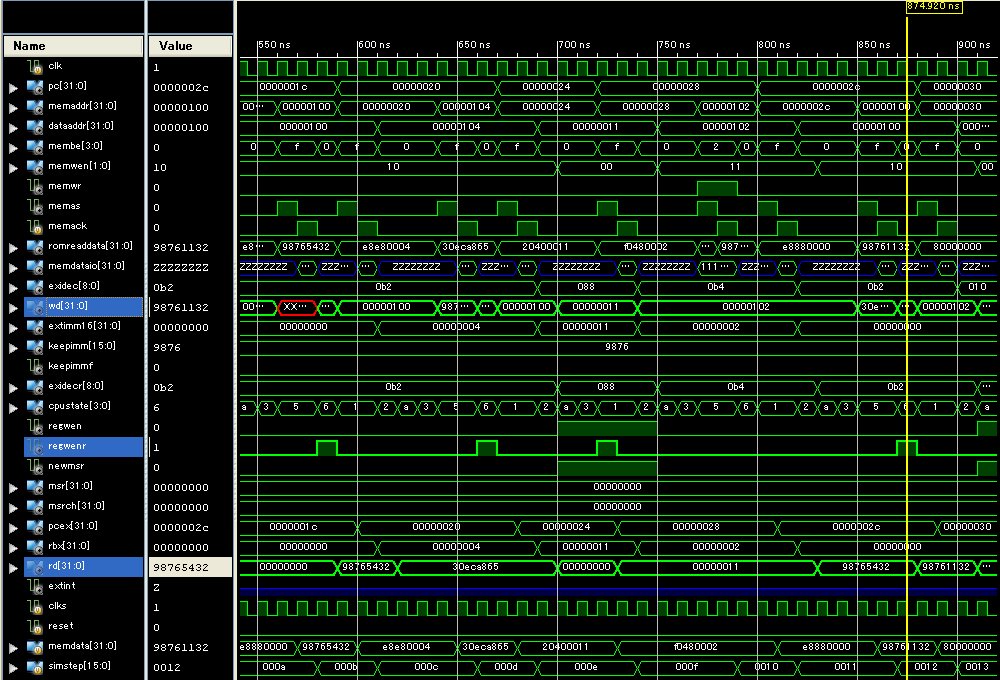

埲壓偼丄ISim 偱僔儈儏儗乕僔儑儞偟偨偲偒偺丄僗僋儕乕儞僔儑僢僩偱偡丅塃偺墿怓偺僇乕僜儖埵抲偼丄乭# 0x100 斣抧偐傜丂0x98761132丂傪 r4 偵撉傓乭偺柦椷傪幚峴偟丄儗僕僗僞偺丄r4 傪彂偒姺偊傞捈慜偱偡丅僴僀儔僀僩偝偣偰偄傞丄 wd[31:0] 偼丄儗僕僗僞傊偺儔僀僩僨乕僞丄regwenr 偼儗僕僗僞傊偺儔僀僩僀僱乕僽儖丄rd[31:0] 偼丄儗僕僗僞 rd 偺撪梕偱偡乮儕傾儖僞僀儉昞帵乯丅儗僕僗僞 rd 偺撪梕偼丄師偺僋儘僢僋偺棫偪忋偑傝偱丄0x98765432丂偐傜丄0x98761132丂偵側偭偰偄傞偺偑妋擣偱偒傑偡丅

倀俙俼俿傪捛壛偟偰侾暥帤傪憲怣偡傞 僜乕僗堦幃 偱偡丅

Xilinx MicroBlaze GAS Listing asmtest.s page 1

1 # Custom MicroBlaze 僥僗僩僾儘僌儔儉丂倀俙俼俿偱侾暥帤憲怣

2 .globl _start

3 .section .vectors.reset, "ax"

4 .align 2

5 _start:

6 0000 B000FFFF addi r8,r0,0xFFFF0007 # UART 偺僨乕僞儗僕僗僞傾僪儗僗

6 21000007

7 0008 20600041 addi r3,r0,'A' # 憲怣暥帤偼丄'A'

8 000c F0680000 sbi r3,r8,0 # UART 偵侾暥帤憲怣梫媮傪弌偡

9 0010 80000000 nop

10 0014 80000000 nop

11 0018 80000000 nop

12 001c 80000000 nop

13 0020 80000000 nop

14 0024 80000000 nop

15 0028 80000000 nop

16 002c 80000000 nop

17 0030 80000000 nop

18 0034 80000000 nop

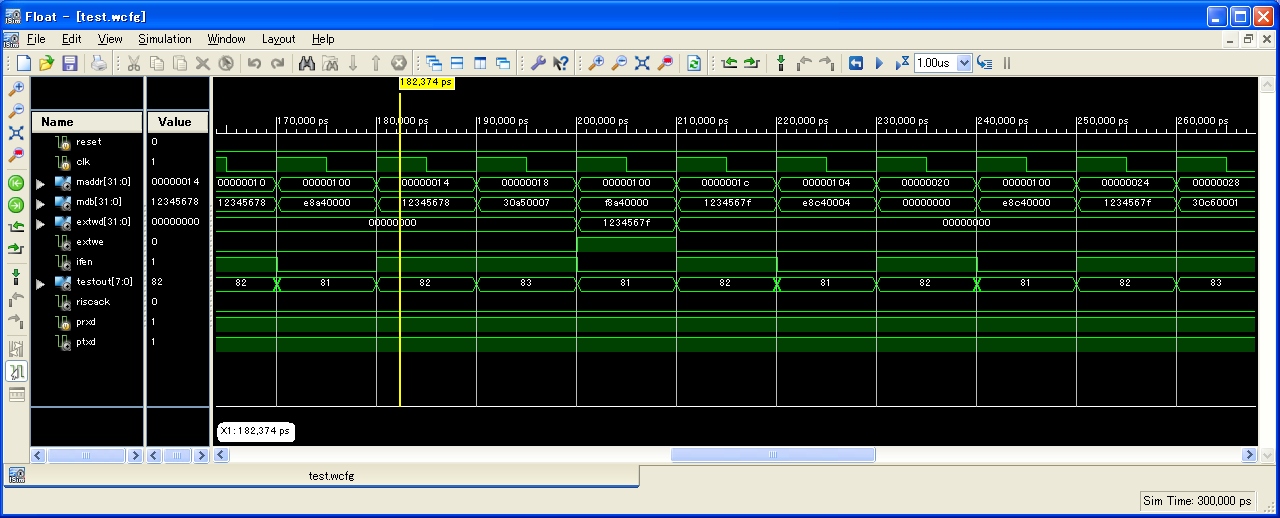

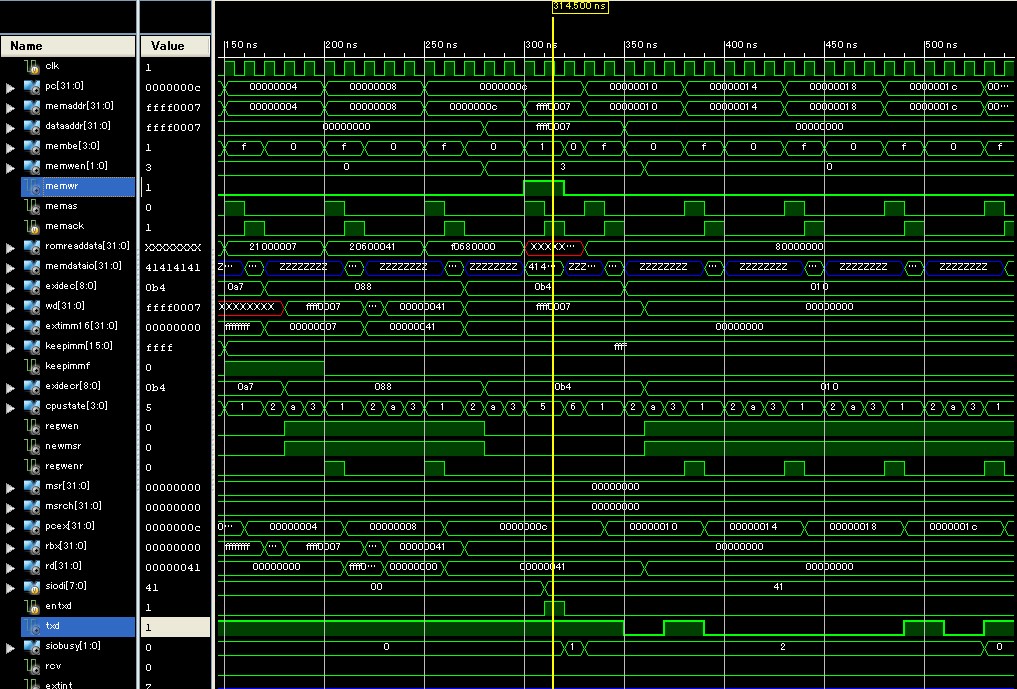

埲壓偼丄ISim 偺僗僋儕乕儞僔儑僢僩偱偡丅僇乕僜儖偺埵抲偱丄倀俙俼俿偺僨乕僞億乕僩偵丄侽倶係侾傪彂偄偰偄傑偡丅倀俙俼俿偐傜偺憲怣攇宍偼丄txd 偱偡丅嵟弶偵俫倝倗倛偐傜俴倧倵偵曄壔偟偰俀僋儘僢僋娫偑丄僗僞乕僩價僢僩丄偦偺屻丄俴俽俛亅亅亜俢侾丆俢俀丆俢俁丆偲懕偒傑偡丅僥僗僩儀儞僠偱倀俙俼俿傊偺愝掕傪俆侽俵倐倫倱偵偟偰偄傞偺偱丄侾價僢僩偑俀僋儘僢僋偱偡丅

俧俠俠僐儞僷僀儔偵懳墳偡傞偺偵昁梫側柦椷偺捛壛偲僥僗僩

俧俠俠僐儞僷僀儔偵懳墳偡傞偺偵昁梫側柦椷偺捛壛偲僥僗僩 僜乕僗堦幃 偱偡丅

# Custom MicroBlaze 丂倀俙俼俿偺憲怣拞僼儔僌傪妋擣偟偰憲怣

.globl _start

.section .vectors.reset, "ax"

.align 2

_start:

brai _start1

.section .vectors.sw_exception, "ax"

.align 2

_vector_sw_exception:

# brai _exception_handler

brai _start1

.section .vectors.interrupt, "ax"

.align 2

_vector_interrupt:

# brai _interrupt_handler

brai _start1

# brai inttest

.section .vectors.hw_exception, "ax"

.align 2

_vector_hw_exception:

# brai _hw_exception_handler

brai _start1

.section .text

_start1:

addi r1,r0,0x1000 # 僗僞僢僋愝掕 r1=0x1000

brai _start2 # 師偺柦椷傪幚峴偣偢偵僽儔儞僠

addi r5,r0,'A' # 憲怣暥帤偼丄'A'

brai loop

_start2:

brlid r15,putcons # 僱僗僥傿儞僌晅偒

addi r5,r0,'H' # 憲怣暥帤偼丄'H'

addi r5,r0,0x114

sra r5,r5 # r5 = 0x8a

sra r5,r5 # r5 = 0x45

loop:

addi r8,r0,0xFFFF0007

braid loop2

sbi r5,r8,0 # UART 偵侾暥帤憲怣梫媮傪弌偡

loop1:

nop

brai loop1

loop2:

brai loop2

# 僒僽儖乕僠儞僥僗僩

# r5 傪 UART 偱憲怣

putcon:

lbui r3,r0,0xFFFF0003 # UART status address

andi r3,r3,6 # D2,D1 busy flag

bnei r3,putcon

sbi r5,r0,0xFFFF0007 # 憲怣

rtsd r15,8 # r15 偺傾僪儗僗偵僽儔儞僠

nop

# 僒僽儖乕僠儞偺僱僗僥傿儞僌

putcons:

addik r1,r1,-4 # 戅旔僄儕傾妋曐

swi r15,r1,0 # 栠傝斣抧戅旔

brlid r15,putcon # r5 傪 UART 偱憲怣

nop

lwi r15,r1,0 # 栠傝斣抧暅婣

rtsd r15,8

addik r1,r1,4 # 僗僞僢僋億僀儞僞傪栠偡

#

偙偺僥僗僩僾儘僌儔儉偱偼丄侽斣抧偐傜 _start1乮儕儞僇僗僋儕僾僩偱丄侽倶俆侽斣抧偲側傞傛偆偵巜帵偟偰偄傞乯 偵旘傃丄僗僞僢僋億僀儞僞傪愝掕偟丄師偵 _start2 偵僽儔儞僠偟傑偡丅偙偺僽儔儞僠柦椷偼丄僨傿儗僀僗儘僢僩柍偟側偺偱丄師偺峴偺丂乭# 憲怣暥帤偼丄'A'丂乭丂偺柦椷偼幚峴偝傟傑偣傫丅

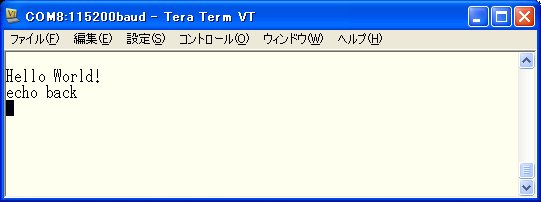

幚婡専徹梡偺俿俷俹儌僕儏乕儖傪嶌惉偟偰丄Hello World!乮 Avnet Spartan6 LX9 MicroBoard 乯

掕斣偺乭Hello World!乭傪弌偟

# Custom MicroBlaze 丂倀俙俼俿偺憲怣拞僼儔僌傪妋擣偟偰丄Hello World! 憲怣

.globl _start

.section .vectors.reset, "ax"

.align 2

_start:

brai _start1

.section .vectors.sw_exception, "ax"

.align 2

_vector_sw_exception:

# brai _exception_handler

brai _start1

.section .vectors.interrupt, "ax"

.align 2

_vector_interrupt:

# brai _interrupt_handler

brai _start1

# brai inttest

.section .vectors.hw_exception, "ax"

.align 2

_vector_hw_exception:

# brai _hw_exception_handler

brai _start1

.section .text

_start1:

addi r1,r0,0x1000 # 僗僞僢僋愝掕 r1=0x1000

brai _start2 # 師偺柦椷傪幚峴偣偢偵僽儔儞僠

addi r5,r0,'A' # 憲怣暥帤偼丄'A'

brai loop

_start2:

brlid r15,putcons # 僱僗僥傿儞僌晅偒

addi r5,r0,'\r' # 憲怣暥帤偼丄'\r'

brlid r15,putcons # 僱僗僥傿儞僌晅偒

addi r5,r0,'\n' # 憲怣暥帤偼丄'\n'

brlid r15,putcons # 僱僗僥傿儞僌晅偒

addi r5,r0,'H' # 憲怣暥帤偼丄'H'

addi r5,r0,0x194

sra r5,r5 # r5 = 0xCA

sra r5,r5 # r5 = 0x65

brlid r15,putcon

nop

brlid r15,putcon

addi r5,r0,'l' # 憲怣暥帤偼丄'l'

brlid r15,putcon

addi r5,r0,'l' # 憲怣暥帤偼丄'l'

brlid r15,putcon

addi r5,r0,'o' # 憲怣暥帤偼丄'o'

brlid r15,putcon

addi r5,r0,' ' # 憲怣暥帤偼丄' ' space

brlid r15,putcon

addi r5,r0,'W' # 憲怣暥帤偼丄'W'

brlid r15,putcon

addi r5,r0,'o' # 憲怣暥帤偼丄'o'

brlid r15,putcon

addi r5,r0,'r' # 憲怣暥帤偼丄'r'

brlid r15,putcon

addi r5,r0,'l' # 憲怣暥帤偼丄'l'

brlid r15,putcon

addi r5,r0,'d' # 憲怣暥帤偼丄'd'

brlid r15,putcon

addi r5,r0,'!' # 憲怣暥帤偼丄'!'

brlid r15,putcons # 僱僗僥傿儞僌晅偒

addi r5,r0,'\r' # 憲怣暥帤偼丄'\r'

brlid r15,putcons # 僱僗僥傿儞僌晅偒

addi r5,r0,'\n' # 憲怣暥帤偼丄'\n'

loop:

brlid r15,getcon # 侾暥帤庴怣偡傞傑偱栠傜側偄

nop #

brlid r15,putcon # r3 偵丄庴怣暥帤

add r5,r0,r3 # r5 偵僐僺乕

brai loop #

nop

# 僒僽儖乕僠儞僥僗僩

# r5 傪 UART 偱憲怣

putcon:

lbui r3,r0,0xFFFF0003 # UART status address

andi r3,r3,6 # D2,D1 busy flag

bnei r3,putcon

sbi r5,r0,0xFFFF0007 # 憲怣

rtsd r15,8 # r15 偺傾僪儗僗偵僽儔儞僠

nop

# 僒僽儖乕僠儞偺僱僗僥傿儞僌

putcons:

addik r1,r1,-4 # 戅旔僄儕傾妋曐

swi r15,r1,0 # 栠傝斣抧戅旔

brlid r15,putcon # r5 傪 UART 偱憲怣

nop

lwi r15,r1,0 # 栠傝斣抧暅婣

rtsd r15,8

addik r1,r1,4 # 僗僞僢僋億僀儞僞傪栠偡

#

# 倀俙俼俿偐傜侾暥帤庴怣偡傞傑偱懸偪丄庴怣偡傞偲暥帤傪 r3 偵儘乕僪偟偰儕僞乕儞

getcon:

lbui r3,r0,0xFFFF0003 # UART status address

andi r3,r3,1 # 侾暥帤庴怣僼儔僌偼丄俴俽俛偺侾價僢僩

beqi r3,getcon

lbui r3,r0,0xFFFF0007 # UART 僨乕僞儗僕僗僞傪撉傓丅撉傓偲丄庴怣僼儔僌偼僋儕傾偝傟傞

rtsd r15,8 # r15 偺傾僪儗僗偵僽儔儞僠

nop

#

hexutils.exe 兝0.17 偙偺僣乕儖偼丄VC++2005 偱嶌惉偟偰偄傞偺偱丄 Microsoft 倁俠亄亄俀侽侽俆梡儔儞僞僀儉 嵞斝晍壜擻僷僢働乕僕 偑昁梫側応崌偑偁傝傑偡丅

NET txd LOC = t7;# USB-serial TX;

NET rxd LOC = r7;# USR-serial RX;

NET clki LOC = k15 ;# 66.66MHz;

NET reset LOC = v4 | PULLDOWN;# SW5

幚婡偱摦嶌偝偣傞僼傽僀儖偼偙偪傜丅 僜乕僗堦幃 偱偡丅

Hello World! 傪昞帵偱偒偨偲偙傠偱丄師偼丄僐儞僷僀儔偱彂偄偨僾儘僌儔儉傪幚峴偝偣傞

儕僙僢僩僗僞乕僩偱憱傞丄傾僙儞僽儔婰弎偺僾儘僌儔儉偐傜丄俠僐儞僷僀儔偱彂偄偨丄main 傪屇傃弌偡傛偆偵捛壛丅

俠僐儞僷僀儔偱巊偆曄悢椞堟偺僋儕傾傪丄傾僙儞僽儔偱婰弎偡傞丅

俠偱彂偄偨僾儘僌儔儉偐傜丄傾僙儞僽儔婰弎偺僒僽儖乕僠儞傪屇傃弌偡僥僗僩傪偡傞丅

俠僐儞僷僀儔偱妱傝崬傒張棟娭悢傪婰弎偟丄僀儞僞乕僶儖僞僀儅偱妱傝崬傒傪敪惗偝偣偰摦嶌偺妋擣傪偡傞丅

俠僐儞僷僀儔偱彂偔僾儘僌儔儉偵丄儊儌儕側偳偺曄峏傗丄擟堄斣抧偐傜偺幚峴偑偱偒傞儌僯僞婡擻傪擖傟丄倀俙俼俿傪夘偟偨僐儅儞僪偱忋婰偺僥僗僩偑偱偒傞傛偆偵偡傞丅

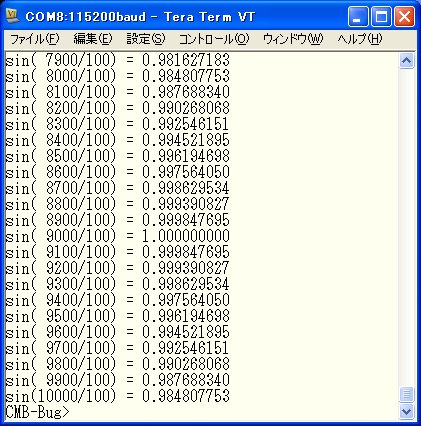

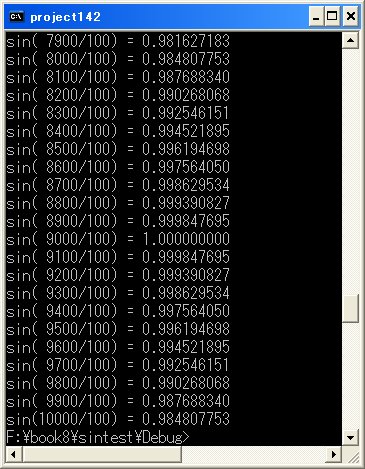

儌僯僞偺憖嶌偲婡擻偼偙偪傜仺丂Custom MicroBlaze 儌僯僞偺憖嶌 偙傟傜傪幚憰偡傞偲丄栺俉侽僗儔僀僗傎偳憹壛偟偰丄俴倃俋偱偼栺俆侾亾偺丂Number of occupied Slices丂偵側傝傑偡丅 僐儞僷僀儔偱彂偄偨僾儘僌儔儉傪幚峴偝偣傞 僜乕僗堦幃 偱偡丅

// sintest.cpp : 僐儞僜乕儖 傾僾儕働乕僔儑儞偺僄儞僩儕 億僀儞僩傪掕媊偟傑偡丅

//

#include "stdafx.h"

#include <math.h>

union i64{

unsigned int i32[2];

unsigned long long ll64;

double fd;

};

#define pai 3.1415926535897932384626433832795028841971

union i64 i64ui,i64ui1,i64ui2,i64ui3,i64ui4;

int mode;

int start,count,step,result;

int _tmain(int argc, _TCHAR* argv[])

{

int i;

if(argc < 5) // sintest mode start count step

{

return 0;

}

sscanf(argv[1],"%ld",&mode);

sscanf(argv[2],"%ld",&start);

sscanf(argv[3],"%ld",&count);

sscanf(argv[4],"%ld",&step);// 0.01 搙扨埵

{

for(i=0;i<count;i++)

{

i64ui.fd = (pai*(start + step*i))/18000.0;

i64ui3.fd = sin(i64ui.fd);

i64ui2.fd = i64ui3.fd*1000000000.0;

result = i64ui2.fd;// 俋寘偺廫恑悢偱惍悢壔丅1000000000 埲奜

if(mode == 0)

{

if(result != 1000000000)

printf("\r\nsin(%5ld/100) = 0.%09ld",(start + step*i),result);

else

printf("\r\nsin(%5ld/100) = 1.000000000",(start + step*i));

}

if(mode == 1)

printf("\r\nsin(%5ld/100) = %08lX %08lX",(start + step*i),i64ui3.i32[1],i64ui3.i32[0]);

}

}

return 0;

}

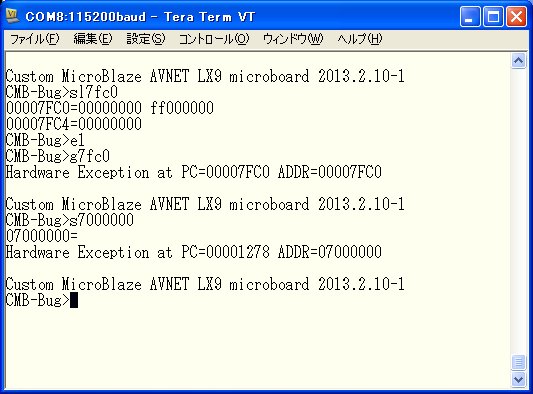

偲婲摦儊僢僙乕僕偑弌偰 sl7fc0 ( enter ) ff000000 ( enter ) 偱俈俥俠侽斣抧傪丄long 偱丄侽倶俥俥侽侽侽侽侽侽丂傪彂偒丄 e1 ( enter ) 偱丄僴乕僪僂僄傾椺奜傪壜擻偵偡傞柦椷丂乮 e1 ) 偱丄俵俽俼偺俤俤儗僕僗僞傪侾偵偟偰丄 g7fc0 ( enter ) 偱俈俥俠侽斣抧傪幚峴偡傞偲丄枹掕媊柦椷側偺偱丄 偲丄Hardware Exception 偑侽倶俈俥俠侽斣抧偱敪惗偟偨偲曬崘偟偰偄傑偡丅 s7000000 ( enter ) 偱丄侽倶俈侽侽侽侽侽侽斣抧偺儊儌儕傪曄峏偟傛偆偲偟偰 丂傾僪儗僗偼昞帵偝傟偨偑丄撪梕偑昞帵偝傟偢丄 偲丄儕乕僪柦椷偺 侽倶侾俀俈俉斣抧偱丄侽倶俈侽侽侽侽侽侽斣抧傪傾僋僙僗偟傛偆偲偟偰丄僶僗僞僀儉傾僂僩偟偰偄傑偡丅

俴俹俢俢俼儊儌儕偱僾儘僌儔儉傪憱傜偣傞乮 Avnet Spartan6 LX9 MicroBoard 乯

弶斉偺 Custom MicroBlaze 偱偼丄僾儘僌儔儉偼僽儘僢僋俼俙俵偵擖傟偰偍偔昁梫偑偁傝傑偟偨偑丄怴婯奐敪斉偱偼奜晹儊儌儕偱摦偐偡偲偄偆偺傪戞侾偺栚昗偲偟偰偄偨偺偱丄偄傛偄傛杮柦偵偲傝偐偐傝傑偡丅崱夞巊偭偨俥俹俧俙偼丄SPARTAN6 LX9 偺俵俬俧偱俢俼俙俵偑巊偊傞昡壙婎斅側偺偱丄LPDDR 儊儌儕傪憖嶌偡傞夞楬傪捛壛偟傑偡丅倃倝倢倝値倶偺俵俠俛偺巊偄曽偼丄 偙偪傜側偳傪嶲峫偵偟偰偄偨偩偄偰丄 CORE Generator偱俴俹俢俢俼偺俬俹傪嶌惉偟傑偡丅俬俹偼丄柤慜傪丄mymig2 偲偟偰暿偺僾儘僕僃僋僩偱嶌惉偟丄昁梫側晹暘乮 ipcore_dir\mymig2\user_design\rtl\ 埲壓偡傋偰乯傪奐敪拞偺僜乕僗偵僼僅儖僟偛偲僐僺乕偡傟偽巊偆偙偲偑偱偒傑偡丅俴俹俢俢俼偺俬俹愝掕偼埲壓偺傛偆偵側傝傑偡丅

Controller Options :

Memory : LPDDR

Interface : NATIVE

Design Clock Frequency : 5000 ps (200.00 MHz)

Memory Type : Components

Memory Part : MT46H32M16XXXX-5

Equivalent Part(s) : MT46H32M16LFBF-5

Row Address : 13

Bank Address : 2

Data Mask : enabled

Memory Options :

Burst Length : 4(010)

CAS Latency : 3

Partial-Array Self Refresh : Full Array

Operation : Normal AR Operation

Drive Strength : Full-Strength

User Interface Parameters :

Configuration Type : One 64-bit bi-directional and two 32-bit bi-directional ports

Ports Selected : Port0, Port1, Port2

Memory Address Mapping : BANK_ROW_COLUMN

Arbitration Algorithm : Round Robin

Arbitration :

Time Slot0 : 012

Time Slot1 : 120

Time Slot2 : 201

Time Slot3 : 012

Time Slot4 : 120

Time Slot5 : 201

Time Slot6 : 012

Time Slot7 : 120

Time Slot8 : 201

Time Slot9 : 012

Time Slot10: 120

Time Slot11: 201

FPGA Options :

Class for Address and Control : II

Class for Data : II

Memory Interface Pin Termination : EXTERN_TERM

DQ/DQS : 25 Ohms

Bypass Calibration : enabled

Debug Signals for Memory Controller : Disable

Input Clock Type : Single-Ended

end else if (C_INPUT_CLK_TYPE == "SINGLE_ENDED") begin: se_input_clk

/* // 偙偺晹暘傪僐儊儞僩

assign sys_clk_ibufg = sys_clk;// 捛壛

localparam C3_CLKOUT0_DIVIDE = 2;

localparam C3_CLKOUT1_DIVIDE = 2;

localparam C3_CLKOUT2_DIVIDE = 16;

localparam C3_CLKOUT3_DIVIDE = 8;

localparam C3_CLKFBOUT_MULT = 4;

localparam C3_DIVCLK_DIVIDE = 1;

localparam C3_CLKOUT0_DIVIDE = 1;

localparam C3_CLKOUT1_DIVIDE = 1;

localparam C3_CLKOUT2_DIVIDE = 4;

localparam C3_CLKOUT3_DIVIDE = 4;

localparam C3_CLKFBOUT_MULT = 4;

localparam C3_DIVCLK_DIVIDE = 1;

偦偺傎偐丄俴俹俢俢俼偵愙懕偝傟傞僺儞偑丄ipcore_dir\mymig2\user_design\par\mymig2.ucf 偲偟偰僕僃僱儗乕僩偝傟偰偄傞偺偱丄偙偺拞恎傪崱傑偱巊偭偰偒偨丂倀俠俥丂僼傽僀儖偵捛壛偟傑偡丅

俴俹俢俢俼儊儌儕惂屼傪幚憰偟偨僜乕僗堦幃 仺丂SRCsmiga.lzh 媽 SRCsmig.lzh 偼儊儌儕僟儞僾側偳偺昞帵偵丄Dhrystone 偺 printf 偺偨傔 cprintf 傪夵憿偟偨偨傔丄懡偔偺僶僌偑偁傝傑偡丅 仺丂媽 SRCsmig.lzh D2710 ( enter )

Microseconds for one run through Dhrystone: 48.6

Dhrystones per Second: 20550

偵側傝丄

CMB-Bug>l ( enter ) g8000000 ( enter ) D2710 ( enter )

偲丄Dhrystone 2.1 偺儖乕僾偑巒傑傝丄

Microseconds for one run through Dhrystone: 249.0

Dhrystones per Second: 4010

偲 栺俀丏俁 倁俙倃俵俬俹俽 偺寢壥傪弌偟傑偡丅俴俹俢俢俼儊儌儕偱偼丄僽儘僢僋俼俙俵偺栺侾乛俆偺僗僺乕僪偵側偭偰偄傑偡丅偙偺僗僺乕僪偼丄挷傋偰傒傞偲丄愄偺俶俤俠偺僷僜僐儞丄俹俠俋俉侽侾俼俙乮 80386 16MHz 僉儍僢僔儏柍偟 DRAM 乯掱搙偱偡丅

僉儍僢僔儏傪幚憰偟偰僗僺乕僪僥僗僩乮 Avnet Spartan6 LX9 MicroBoard 乯

Dhrystoe 2.1

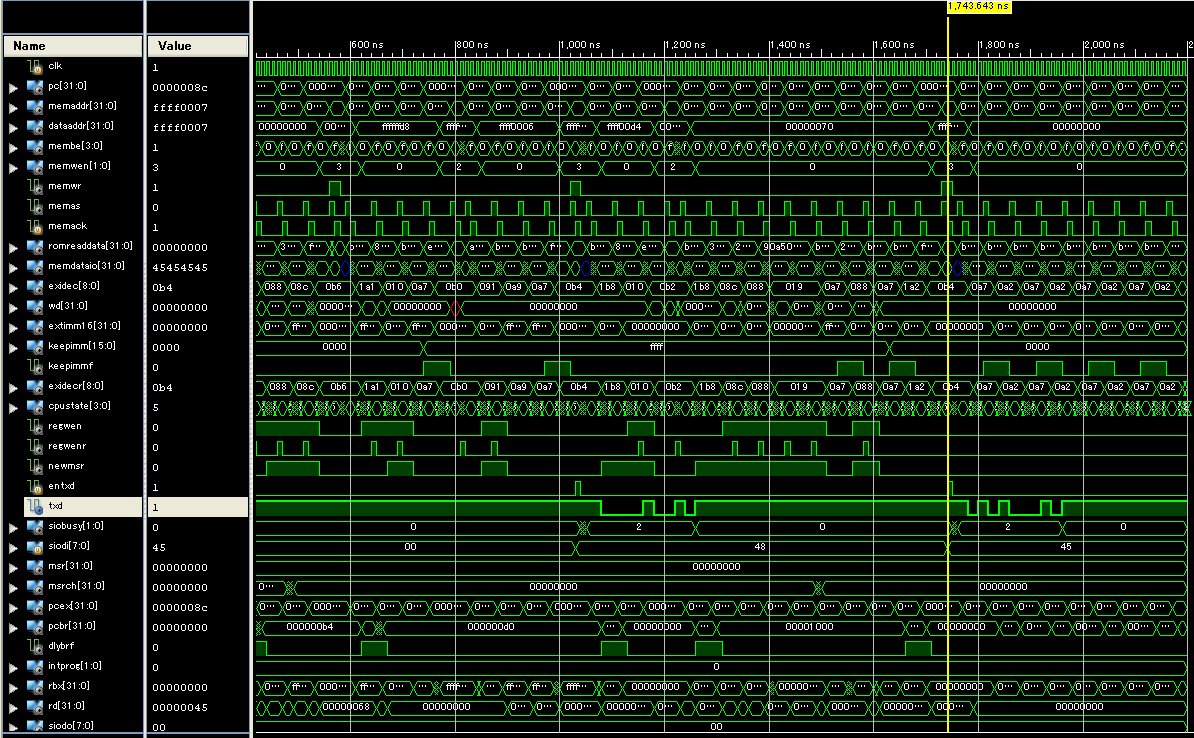

俠俹倀偲摦嶌忦審

丂Dhrystones per Second丂 丂倁俙倃俵俬俹俽丂

risc4s BRAM gcc 4.6.2

丂俀侽俆俆侽丂 丂侾侾丏俇俋丂

risc4s LPDDR 儊儌儕 gcc 4.6.2

丂係侽侾侽丂 丂俀丏俁丂

RX62N 96MHz( 撪憼 俼俙俵 ) gcc 4.6.0

丂侾侾俋俁俁侽丂 丂俇俈丏俋丂

SH7144(SH2) 48MHz( 奜晹 16bit SRAM ) gcc 4.0.2

丂栺俀俆侽侽丂 丂栺侾丏係丂 SH7750(SH4) 240MHz( 奜晹 32bit SDRAM 80MHz) cache OFF gcc 4.6.0

丂俋俆俀俈丂 丂俆丏係丂 SH7750(SH4) 240MHz( 奜晹 32bit SDRAM 80MHz) cache ON gcc 4.6.0

丂俁俆係俇侽俋丂 丂俀侽侾丏俉丂

偪傚偭偲敾掕偺曽朄傪曄偊傞偩偗偱丄俆亾傎偳憹偊偨傝尭偭偨傝偡傞傛偆偱偡丅

Custom MicroBlaze AVNET LX9 microboard 2013.2.24-1

CMB-Bug>c ( enter ) c1 ( enter ) c3 ( enter ) sla100000 ( enter ) 30601234 ( enter ) b60f0008 ( enter ) 80000000 ( enter ) 30609876 ( enter ) b60f0008 ( enter ) 80000000 ( enter ) 僐儞僩儘乕儖俠 g8100000 ( enter ) g8100010 ( enter ) swa100002 ( enter ) 僐儞僩儘乕儖俠 swa100012( enter ) 僐儞僩儘乕儖俠 g8100000 ( enter ) g8100010 ( enter ) d8100000,8100020 ( enter ) r3 偵偼丄0x4321 丄傑偨丄0x6789 偑儘乕僪偝傟傞柦椷偵側偭偰偄傑偡

CMB-Bug>d6002800,6002820 ( enter ) 僞僌儊儌儕偼丄侾俇價僢僩偱偡偑丄俉僶僀僩嫬奅乮儔僀儞僒僀僘乯偵攝抲偟偰昞帵偱偒傞傛偆偵偟偰偄傑偡

丂丂偙偙偱丄柦椷僉儍僢僔儏偵撉傫偩椞堟傪柍岠壔偡傞偨傔丄

丂丂"cii" 柦椷偱丄0x8100000 偐傜丄0x10 僶僀僩柍岠偵偟傑偡 cache invalidate instruction cii8100000,10 ( enter ) d6002800,6002820( enter ) 柍岠壔偟偨偺偱丄嵞搙幚峴偟偰傒傑偡 崱搙偼丄曄峏屻偺柦椷傪幚峴偟偨偺偱丄0x4321 偲側偭偰偄傑偡 柍岠壔偟偰偄側偄曽偼埲慜偺傑傑偱偡 柍岠壔偝傟偨偺偱丄俢俼俙俵偐傜嵞搙撉傫偱峏怴偟偨偺偱丄惓偟偄寢壥偵側傝傑偡

埲忋偺僉儍僢僔儏傪幚憰偟偨僜乕僗堦幃仺丂 SRCs_cache.lzh

Dhrystoe 2.1

摦嶌忦審 丂Dhrystones per Second丂 丂倁俙倃俵俬俹俽丂

risc4s BRAM gcc 4.6.2

丂俀侽俆俆侽丂 丂侾侾丏俇俋丂

risc4s LPDDR 儊儌儕 媽夞楬

丂係侽侾侽丂 丂俀丏俁丂

risc4s LPDDR 儊儌儕 僉儍僢僔儏幚憰丂cache OFF

丂係俋俈侽丂 丂俀丏俉丂

risc4s LPDDR 儊儌儕 僉儍僢僔儏幚憰丂d-cache ON

丂俇係俁侽丂 丂俁丏俇俇丂 risc4s LPDDR 儊儌儕 僉儍僢僔儏幚憰丂i-cache ON

丂俈侽俉侽丂 丂係丏侽俁丂 risc4s LPDDR 儊儌儕 僉儍僢僔儏幚憰丂i-cache d-cache ON

丂侾侾侽俆侽丂 丂俇丏俀俋丂

丂俽俹俬儊儌儕傪憖嶌偟偰傒傞乮 Avnet Spartan6 LX9 MicroBoard 乯

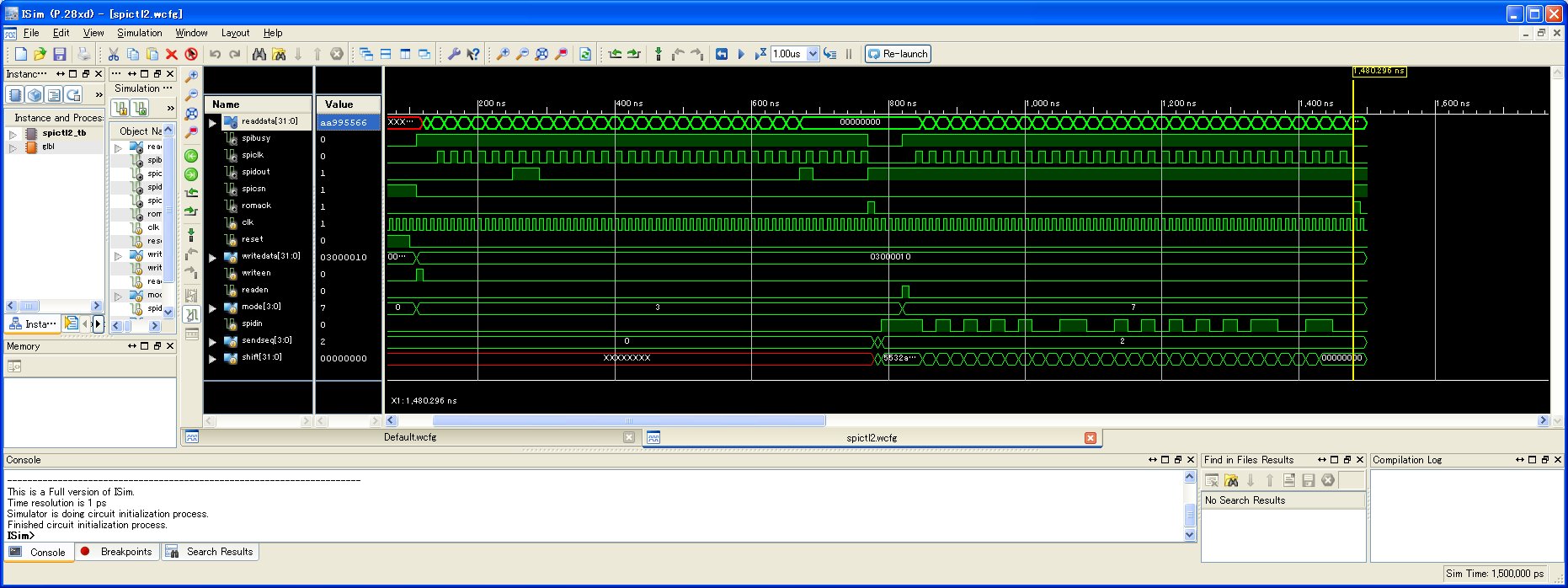

俽俹俬儊儌儕惂屼傪幚憰偟偨僜乕僗堦幃 仺丂SRCsspi.lzh 2013.3.3 hexutils download丂 儐乕僓乕搊榐丄儘僌僀儞偑昁梫

俥俹俧俙偺僐儞僼傿僊儏儗乕僔儑儞偵巊偭偰傞偺偱丄儔僀僩偺僥僗僩偼怲廳偝偑梫傝傑偡丅幚嵺丄僥僗僩拞偵俥俹俧俙偺 bit 僨乕僞偺堦晹傪攋夡偟偰偟傑偭偨偺偱丄俹倧倵倕倰俷俶婲摦偑偱偒側偔側偭偰偟傑偄傑偟偨丅

// simple spi control

module spictl2(

clk,

writedata,

writeen,

mode,

readdata,

readen,

romaddr,

romack,

spibusy,

spiclk,

spidout,

spidin,

spicsn,

reset

);

input clk;

input [31:0] writedata;

input writeen;

input [3:0] mode;

output [31:0] readdata;

input readen;

input [27:0] romaddr;

output romack;

output spibusy;

output spiclk; // 50MHz

output spidout; // 俽俹俬僐儅儞僪丄僨乕僞弌椡

input spidin; // 儊儌儕偐傜偺僨乕僞

output spicsn; // SPI chip select

input reset;

//

reg [3:0] spiseq;

reg [5:0] spishiftcount;

reg [5:0] bitcount;

reg [31:0] spishiftr;

reg spiclkr;

reg spidoutr;

reg spicsnr;

reg spibusy;

reg romack;

assign spiclk = spiclkr;

assign spidout = spidoutr;

assign spicsn = spicsnr;

assign readdata = spishiftr;

always@(posedge clk)

begin

if(reset)

begin

spiseq <= 0;

spicsnr <= 1;

spiclkr <= 0;

spidoutr <= 0;

spibusy <= 0;

romack <= 0;

end

else

begin

if(writeen)

begin

spiseq <= 1;//丂儔僀僩 儕乕僪 儔僀僩僶僀僩悢愝掕 係僶僀僩俁俀價僢僩 mode[2] == 1 偱丄俠俽傪俫倝倗倛偵偟偰廔傝 儕乕僪僶僀僩悢愝掕 係僶僀僩俁俀價僢僩 mode[2] == 1 偱丄俠俽傪俫倝倗倛偵偟偰廔傝

module spictl2_tb;

`timescale 1ns/1ns

reg clk; // risc4s

reg reset;

reg [31:0] writedata;

reg writeen;

reg readen;

reg [3:0] mode;

wire [31:0] readdata;

wire spibusy;

wire spiclk;

wire spidout;

reg spidin;

wire spicsn;

wire romack;

reg [3:0] sendseq;

reg [31:0] shift;

always

begin

#5 clk = 0;

#5 clk = 1;

end

initial

begin

reset = 1; clk = 1; writedata = 0; writeen = 0;// romadr = 0;

readen = 0; mode = 0; spidin = 0;

#100 reset = 0;

#10 writedata = 32'h03000010; writeen = 1; mode = 3;

#10 writeen = 0;

#700 readen = 1; mode = 7;

#10 readen = 0;

end

always@(posedge clk)

begin

if(reset)

begin

sendseq <= 0;

end

else

begin

if((romack)&&(mode == 3))

begin

sendseq <= 1;

shift <= 32'hAA995566;

end

case(sendseq)

1:begin

shift <= {shift[30:0],1'b0};

spidin <= shift[31];

sendseq <= 2;

end

2:begin

if(spiclk)

begin

shift <= {shift[30:0],1'b0};

spidin <= shift[31];

end

end

endcase

end

end

spictl2 u1(

.clk(clk),

.writedata(writedata),

.writeen(writeen),

.mode(mode),

.readdata(readdata),

.readen(readen),

.romaddr(),

.romack(romack),

.spibusy(spibusy),

.spiclk(spiclk),

.spidout(spidout),

.spidin(spidin),

.spicsn(spicsn),

.reset(reset)

);

endmodule

俽俹俬儊儌儕憖嶌僐儅儞僪 儔僀僩丄僀儗乕僘帪偵丄嬛巭椞堟寈崘晅偒乮岺応弌壸帪偺僨乕僞僄儕傾乯

憖嶌撪梕

丂柦椷丂 丂夝愢丂

丂儕乕僪丂

丂rr500000,8100000,1000丂 丂SPI memory 偺0x500000 斣抧偐傜丄DRAM 偺0x8100000 斣抧偵丄0x1000 僶僀僩撉傒弌偡丂

丂儔僀僩丂

丂rw500000,8100000,1000丂 丂SPI memory 偺0x500000 斣抧偵丄DRAM 偺0x8100000 斣抧偐傜丄0x1000 僶僀僩彂偔丂 丂僀儗乕僘丂

丂re500000,3800丂 丂SPI memory 偺0x500000 斣抧偐傜丄0x4000 僶僀僩徚偡丅係倠僶僀僩扨埵丂

俽俹俬儊儌儕憖嶌僐儅儞僪 儔僀僩丄僀儗乕僘帪偵丄嬛巭椞堟寈崘側偟

憖嶌撪梕

丂柦椷丂 丂夝愢丂

丂儔僀僩丂

丂rW500000,8100000,1000丂 丂SPI memory 偺0x500000 斣抧偵丄DRAM 偺0x8100000 斣抧偐傜丄0x1000 僶僀僩彂偔丂

丂僀儗乕僘丂

丂rE500000,3800丂 丂SPI memory 偺0x500000 斣抧偐傜丄0x4000 僶僀僩徚偡丅係倠僶僀僩扨埵丂

Xilinx 偺 .ngc 僼傽僀儖傪嶌惉偟偰丄俠俹倀僜乕僗傪僱僢僩儕僗僩偵曄姺 僀乕僒僱僢僩俹俫倄傪俥俹俧俙偱憖嶌偟偰傒傞丅俵俙俠偺愝寁乮 Avnet Spartan6 LX9 MicroBoard 乯 弨旛拞 弨旛偡傞傕偺

Windows 忋偱Linux 娐嫬傪嶌傞丅 Cygwin

MicroBlaze 偺僐儞僷僀儔僜乕僗 Xilinx 忢偵嵟怴丅俤俢俲傪巊傢側偄応崌偳傟偱傕偄偄丅

俤俢俲偺倁俉丏俀偺僜乕僗偼偡偱偵岞奐傪掆巭偟偰偄傑偡偑丄屆偄 fullsrc.tar.gz 偼偙偙 偵巆偟偰偄傑偡丅

Cygwin 偺僟僂儞儘乕僪

Cygwin 偼丄僟僂儞儘乕僪偟側偑傜僀儞僗僩乕儖偱偒傑偡偑丄慡晹僟僂儞儘乕僪偟偰偐傜丄僨傿僗僋忋偺僨乕僞偐傜僀儞僗僩乕儖偡傞傎偆偑栤戣偑敪惗偟偵偔偄偺偱丄傑偢僟僂儞儘乕僪偺傒 愭偵峴偄傑偡丅偙傟偼丄Cygwin 偺僟僂儞儘乕僪偼丄搑拞偱僷僢働乕僕傪撉傒旘偽偟偰偟傑偭偰丄昁梫側僼傽僀儖傪慡晹僟僂儞儘乕僪偱偒側偄偙偲偑偁傞偐傜偱偡丅偦偟偰敳偗偨僼傽僀儖偑偁偭偰傕丄僀儞僗僩乕儖拞偵寈崘偑弌側偄偙偲偑偁傞偺偱丄僀儞僗僩乕儖偑廔偭偰傕惓忢偵摦嶌偟側偄偙偲偑偁傝傑偡丅摿偵僋儘僗僐儞僷僀儔傪價儖僪偡傞偲偒偵偼丄懡偔偺僷僢働乕僕僜僼僩傪巊偆偺偱丄file not found 偲偐偺儊僢僙乕僕偑弌偰丄搑拞偱僄儔乕偱巭傑偭偰偟傑偆偙偲偑偁傝傑偡丅柍榑丄僋儘僗僐儞僷僀儔傪價儖僪偡傞偵偼丄 configure 偺僆僾僔儑儞愝掕 傪娫堘偊偰僄儔乕偱巭傑傞偙偲傕偟偽偟偽側偺偱丄僄儔乕偺尨場偑僷僢働乕僕晄懌偵傛傞傕偺側偺偐丄configure 偺愝掕晄懌傗巜帵娫堘偄側偺偐丄僄儔乕儊僢僙乕僕偐傜敾撉偡傞偺偼丄姷傟偰偙側偄偲娙扨偵偱偒傑偣傫丅Cygwin 偺僙僢僩傾僢僾

丂Cygwin 偼丄奐敪娐嫬偵偡傞偺偱丄 恾 Devel 慖戰 傪僋儕僢僋偟偰 Install 偵曄偊丄師傊傪僋儕僢僋丅

™ 偼丄Xilinx, Inc.偺彜昗傑偨偼搊榐彜昗偱偡丅

俥俹俧俙偺俠俹倀娭楢

椺侾丗僔儕僐儞僨僓僀儞僥僋僲儘僕乕 僨僓僀儞僂僄乕僽儅僈僕儞俀侽侽俆擭侾寧崋宖嵹婰帠偑偁傞丅C1601 CPUHDL Simulator Veritak verilog僔儈儏儗乕僞丄VHDL --> verilog 曄姺僣乕儖偺斕攧儂乕儉偵栠傞

SEO