|

XilinxのDDR用プリミティブを使わないでDDRメモリを操作してみる

|

SPARTAN3など、XilinxのFPGAには、DDRメモリなどを操作するための、ダブルデータレート専用フリップフロップが内臓されていて、( IFDDRCPE OFDDRTCPE など )DCMと組み合わせて、容易にDDRメモリ( DDR2を含む )とインターフェイスすることができます。SPARTAN6以降は、さらに高速なDDR3などを制御するため、ハードマクロ化されて、800Mbps、さらにKintex7では、1866Mbpsまで可能になっています。

さて、DDRメモリ以降、内蔵のDDR専用フリップフロップを使うと、I/Oピンも専用になり、メモリとの接続を間違えると、インプリメントできなくなることがあります。さらにSPARTAN6では、ハードマクロのMCBを使うと、メモリと接続するピンがすべて決められていて、指定ピン以外を使うことはできません。無論これは、設計を容易にしてくれますが、逆に融通がきかなくなってしまいます。

FPGAを使ったボード設計で、いつも悩むのは、<ピン数をどれだけ減らせるか>ではないかと思います。より小さなパッケージを使って、実装面積を減らす要求は、大抵優先順位が高く、ピンの割り振りには苦労します。

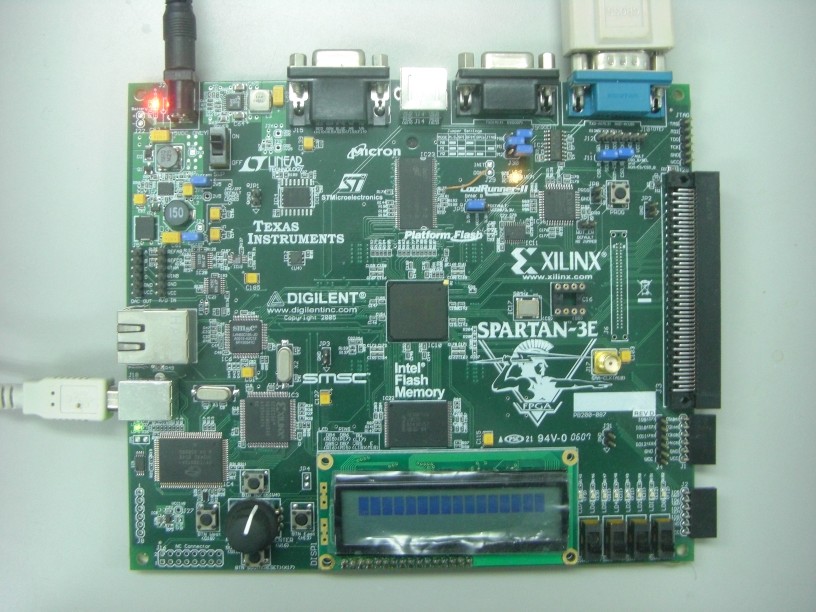

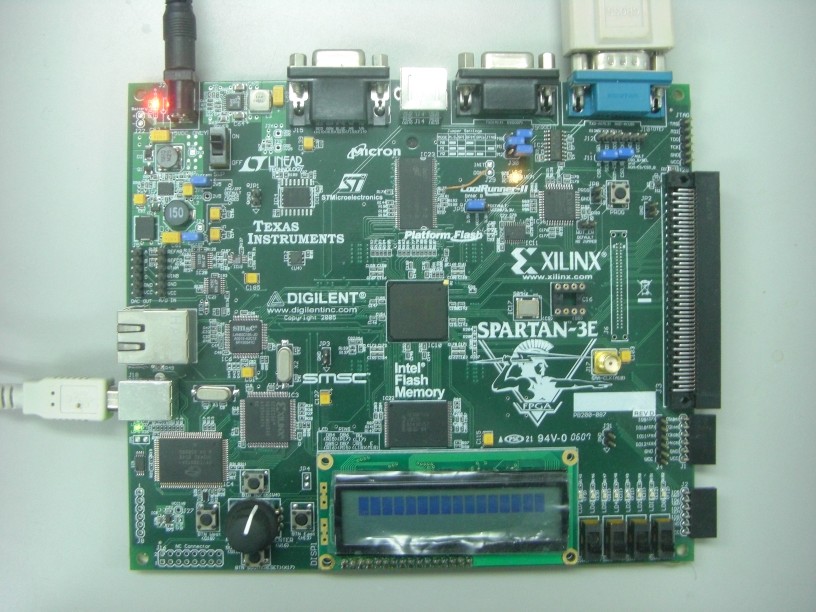

そこで、DDR専用プリミティブを使わないで、DDRメモリを操作する回路を作ってみました。以前、DDRメモリの接続を間違えたボードを、この方法で、何とか使えるようにして、基板改版までボードを捨てずに済んだことがありますが、その回路を、DDRメモリの載った評価ボードにインプリメントしてみました。使用した評価ボードは、Digilent社の、Spartan-3E Sterter Kit です。

このボードは、DDRメモリ、100MのイーサネットPHYなどがあって、EDKのサンプル回路が、選択に出てくるものです。水晶は50MHzになっていて、EDKでは、MicroBlazeを50MHzで操作できます。このとき、DDRメモリは100MHzで動きます。

しかし、回路図を見ると、DDRメモリを接続している部分が、定石から外れていて、終端抵抗も無く、かなり使いにくいボードです。 DDRメモリとは、75オーム( 付けるなら22オームぐらいが定番 )のダンピング抵抗で接続されているので、高速に動作させるのは困難です。EDKでは、このあたりを、DELAY回路を使って、チューニングされたような ucf ソースを吐き出し、100MHzで動かしていますが、EDKを使わずに、IFDDRCPE と OFDDRTCPE と、DCM を使って、100MHzで動かすのはかなり大変です。何度か試みましたが、いまだに66MHz( DDR-133 )までしか動かしたことはありません。

DDRについては、定番の終端抵抗を付けた回路で、Spartan3 で133MHz付近( DDR-266 )まで問題なく動作させたことがありますが、このボードではとても無理です。

このボードで、IFDDRCPE と OFDDRTCPE を使わないで、Verilog の reg 宣言のみを使ってDDRメモリを操作してみます。速さは期待できないので、50MHzとします。操作回路は、100MHzとなりますが、FPGAの能力からすると、133MHzぐらいは動くかもしれません。いわゆるDDRメモリ操作に必要な、90°位相差は、100MHzの逆相クロックで実現します。

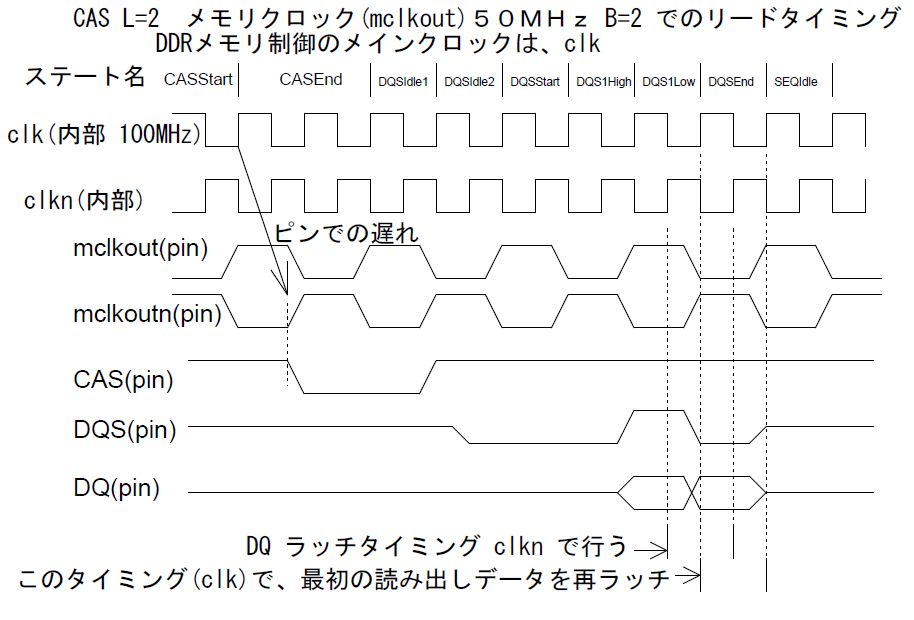

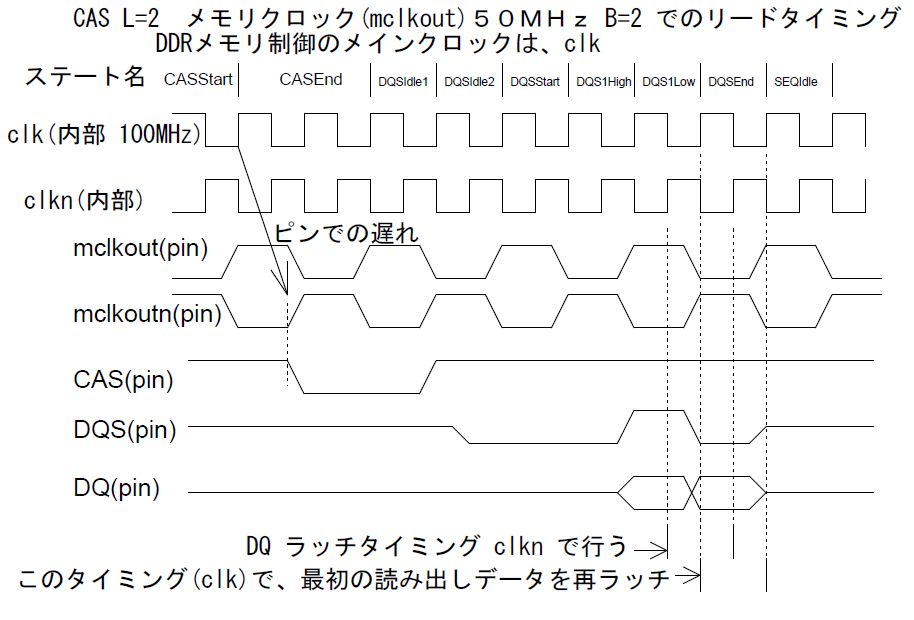

以下の図は、100MHzのDDRメモリ制御回路の予想波形です。これに合わせて、RTLを書いてみます。

この波形を念頭にして、作成した回路は、以下のようになります。

上記の制御回路を確かめるための、テストベンチは以下。論理シミュレーションのみのテストベンチなので、DDRをリードする場合に、1クロックデータを遅らせています。

以上ですが、これらをまとめたISEのプロジェクトファイル一式は以下です。

XilinxのDDR用プリミティブを使わないでDDRメモリを操作 ISE 13.1のISimプロジェクトファイル。

インプリメントする前のもので、完成後の bit ファイルを入れています。この回路は、メモリクロックを66MHzで操作するため、FPGAのメモリ操作RTLは133MHzにしていますが、かろうじて動いているようで、回路を追加すると、133MHzでは動かなくなるようです。

操作ソフトのソース( Cygwin )と、実行可能ヘキサファイルから、FPGAのメモリ初期化データに変換する、binutils も含んでいます。

また Spartan-3E Sterter Kit で動作する、ボード用ソース一式も含んでいます。Custom MicroBlaze でメモリの読み書きができます。操作はRS232Cを使って、パソコンのターミナルソフトで行います。インプリメントに関しては、カスタム設計の MicroBlazeを参考にしてください。

上記の、bit ファイルでコンフィギュレーションすると、基板のJ10に接続したRS232C(クロスケーブル)を介して、パソコンのターミナルソフトには、

Custom MicroBlaze DDR test 2011.12.4

CMB-Bug>

と表示されて、操作待ちになります。以下は、操作待ちになった後、2箇所の領域にデータを書き、一致を調べて、先頭のデータをダンプさせたスクリーンショットです。

この操作で、sl70000000,12345677,100000,30f6a913 は、メモリの0x70000000番地から、初期値を0x12345677として、0x30F6A913を初期値にロングワードで加算しながら0x100000回、アドレスをロングワード単位に更新しながら書くという命令です。異なるアドレスに同じ操作をすれば、4Mバイトまで同じデータになるので、後で、v コマンドで、4Mバイト比較しています。違いが見つかれば、そのつど違いを表示するので、何もなければ、4Mバイトまで一致していることになります。

最後の d70000000 は、0x70000000番地から、128バイトをダンプするコマンドです。

準備中

ホームに戻る