| 傾僪儗僗偲夞楬曄悢柤側偳 |

僒僀僘 |

婡擻 |

| 0xE0000034丂p0_cmd_byte_addri |

32 bit |

俢俢俼俀儊儌儕偺愭摢傾僪儗僗丅俴俽俛偺侾俁價僢僩偼柍帇偝傟傞乮侽偲偡傞乯 |

| 0xE0000038丂loopcountb |

32 bit |

儊儌儕僠僃僢僋偺儖乕僾夞悢丅弶婜偺夞楬梡偱丄埲壓偺僐儅儞僪傪巊梡偡傞偲偒偼侽偲偡傞 |

| 0xE000003C丂dmamode |

32 bit |

俢俢俼俀儊儌儕偺憖嶌僐儅儞僪丅僶僢僼傽乕儊儌儕偺傒傪懳徾偲偡傞柦椷傕偁傞 |

| 0xE0000050丂comperrorcount |

LSB 10 bit |

儊儌儕斾妑偺僄儔乕屄悢丅侾俇僶僀僩扨埵偺斾妑偱堎側傟偽僾儔僗侾偝傟傞 |

| 0xE0000054丂genseed |

32 bit |

儊儌儕偵彂偔嵟弶偺僨乕僞偺弶婜抣偺尦丅侽斣抧偺僨乕僞偼丄偙偺抣偑壛嶼偝傟偨傕偺偵側傞 |

| 0xE0000058丂genadd |

32 bit |

侾俇僶僀僩扨埵偺傾僪儗僗峏怴偱丄偙偺抣偑丂genseed 偵壛嶼偝傟傞 |

| 0xE0000080丂reset_mig |

俴俽俛丂1 bit |

侾傪彂偔偲丄俵俠俛傪儕僙僢僩偟偰俢俢俼俀偺憖嶌傪掆巭忬懺偵偡傞丅侽偱俵俠俛僗僞乕僩 |

| 0xE0000084丂carib_donecount |

32 bit |

俵俠俛偑僗僞乕僩偟偰偐傜丄僉儍儕僽儗乕僔儑儞偑廔傢傞傑偱偺僔僗僥儉僋儘僢僋悢丅 |

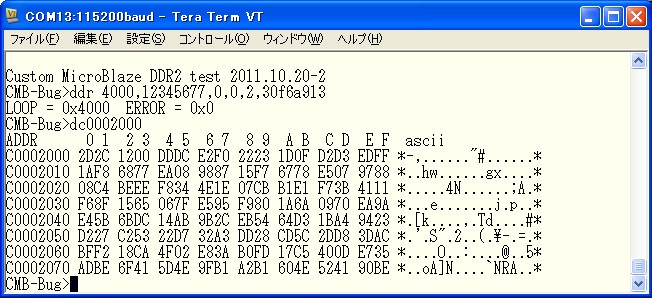

| 0xC0000000丂mem32_128 mem1 |

俉倠俛 |

俢俢俼俀儊儌儕傊彂偔僨乕僞僶僢僼傽乕丅RAMB16_S9_S36 傪係屄巊梡 |

| 0xC0002000丂mem32_128 mem2 |

俉倠俛 |

俢俢俼俀儊儌儕偐傜撉傒弌偡僶僢僼傽乕丅RAMB16_S9_S36 傪係屄巊梡 |